- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371785 > HCTS109DMSR (HARRIS SEMICONDUCTOR) Radiation Hardened Dual JK Flip Flop PDF資料下載

參數(shù)資料

| 型號: | HCTS109DMSR |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | Radiation Hardened Dual JK Flip Flop |

| 中文描述: | HCT SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

| 文件頁數(shù): | 4/9頁 |

| 文件大?。?/td> | 170K |

| 代理商: | HCTS109DMSR |

13

Specifications HCTS109MS

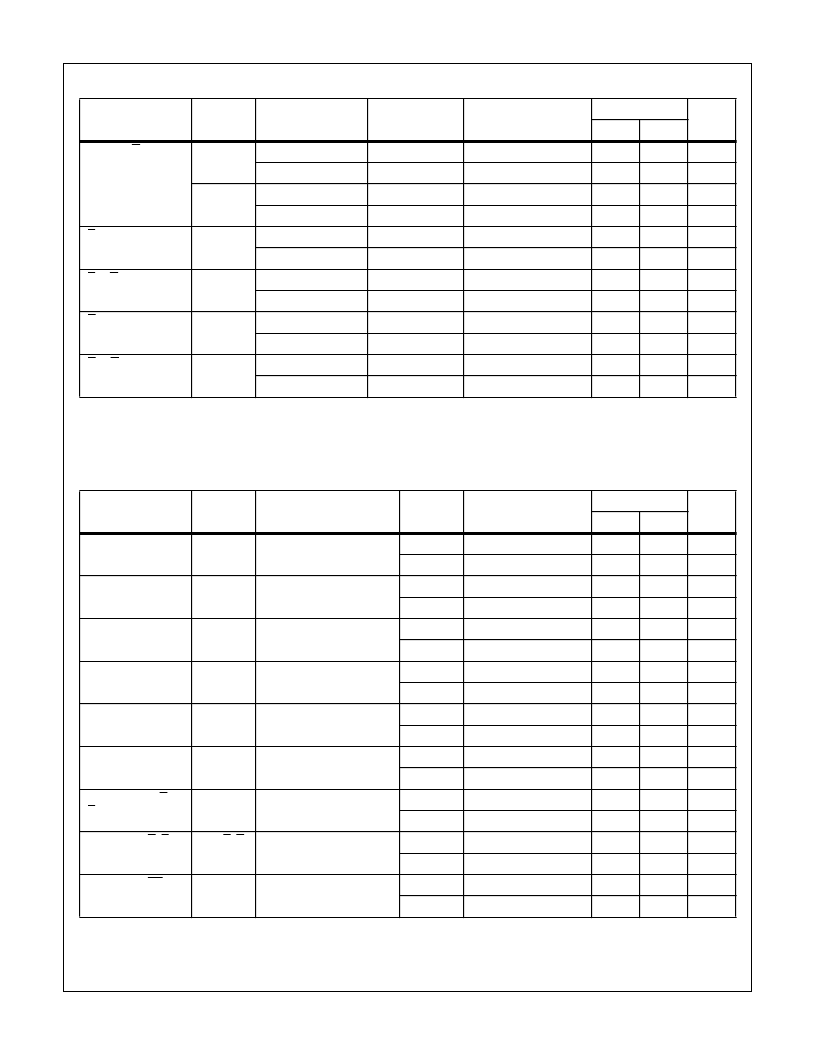

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER

SYMBOL

(NOTES 1, 2)

CONDITIONS

GROUP A

SUBGROUPS

TEMPERATURE

LIMITS

UNITS

MIN

MAX

CP to Q, Q

TPLH

VCC = 4.5V

9

+25

o

C

2

26

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

30

ns

TPHL

VCC = 4.5V

9

+25

o

C

2

30

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

35

ns

S to Q

TPLH

VCC = 4.5V

9

+25

o

C

2

19

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

23

ns

S to Q

TPHL

VCC = 4.5V

9

+25

o

C

2

31

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

33

ns

R to Q

TPHL

VCC = 4.5V

9

+25

o

C

2

31

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

33

ns

R to Q

TPLH

VCC = 4.5V

9

+25

o

C

2

31

ns

VCC = 4.5V

10, 11

+125

o

C, -55

o

C

2

33

ns

NOTES:

1. All voltages referenced to device GND.

2. AC measurements assume RL = 500

, CL = 50pF, Input TR = TF = 3ns, VIL = GND, VIH = 3V.

TABLE 3.

ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

LIMITS

UNITS

MIN

MAX

Capacitance Power

Dissipation

CPD

VCC = 5.0V, f = 1MHz

1

+25

o

C

-

80

pF

1

+125

o

C, -55

o

C

-

82

pF

Input Capacitance

CIN

VCC = 5.0V, f = 1MHz

1

+25

o

C

-

10

pF

1

+125

o

C, -55

o

C

-

10

pF

Output Transition

Time

TTHL

TTLH

VCC = 4.5V

1

+25

o

C

-

15

ns

1

+125

o

C, -55

o

C

-

22

ns

Max Operating

Frequency

FMAX

VCC = 4.5V

1

+25

o

C

-

27

MHz

1

+125

o

C, -55

o

C

-

18

MHz

Setup Time J, K to

CP

TSU

VCC = 4.5V

1

+25

o

C

16

-

ns

1

+125

o

C, -55

o

C

18

-

ns

Hold Time J, K to CP

TH

VCC = 4.5V

1

+25

o

C

3

-

ns

1

+125

o

C, -55

o

C

3

-

ns

Removal Time R,

S to CP

TREM

VCC = 4.5V

1

+25

o

C

16

-

ns

1

+125

o

C, -55

o

C

18

-

ns

Pulse Width R, S

TW (S, R)

VCC = 4.5V

1

+25

o

C

16

-

ns

1

+125

o

C, -55

o

C

18

-

ns

Pulse Width CP

TW (CP)

VCC = 4.5V

1

+25

o

C

24

-

ns

1

+125

o

C, -55

o

C

27

-

ns

NOTE:

1. The parameters listed in Table 3 are controlled via design or process parameters. Min and Max Limits are guaranteed but not directly

tested. These parameters are characterized upon initial design release and upon design changes which affect these characteristics.

Spec Number

518601

相關PDF資料 |

PDF描述 |

|---|---|

| HCTS109DTR | Radiation Hardened Dual JK Flip Flop |

| HCTS109KMSR | Radiation Hardened Dual JK Flip Flop |

| HCTS109MS | Dual Positive-Edge-Triggered D-Type- Flip-Flops With Clear And Preset 14-CDIP -55 to 125 |

| HCTS109T | Dual Positive-Edge-Triggered D-Type- Flip-Flops With Clear And Preset 14-CFP -55 to 125 |

| HCTS109D | Radiation Hardened Dual JK Flip Flop |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HCTS109DTR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual JK Flip Flop |

| HCTS109HMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual JK Flip Flop |

| HCTS109K | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual JK Flip Flop |

| HCTS109KMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual JK Flip Flop |

| HCTS109KTR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual JK Flip Flop |

發(fā)布緊急采購,3分鐘左右您將得到回復。