- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370470 > HD66321 (Hitachi,Ltd.) Multiscan 258-Channel Gate Driver(多掃描258通道門驅(qū)動器) PDF資料下載

參數(shù)資料

| 型號: | HD66321 |

| 廠商: | Hitachi,Ltd. |

| 英文描述: | Multiscan 258-Channel Gate Driver(多掃描258通道門驅(qū)動器) |

| 中文描述: | 多掃描258通道柵極驅(qū)動器(多掃描258通道門驅(qū)動器) |

| 文件頁數(shù): | 5/34頁 |

| 文件大小: | 106K |

| 代理商: | HD66321 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

HD66321

5

Signal Name

Quantity

Input/Output

Function

DL0

DL1

DR0

DR1

4

Input/output

Pins used for scanning signals input or output to the next-

stage IC. Switching between input and output is performed

by the scanning signal shift direction switching signal, SHL,

as shown below.

When SHL = 0, input the scanning signal to DL0 of the first-

stage IC. Fix DL1 low, or, if necessary, input to DL1 the

same signal as the one input to DL0. Connect output DR0

to DL0, and output DR1 to DL1, of the next-stage IC.

When SHL = 1, input the scanning signal to DR0 of the first-

stage IC. Fix DR1 low, or, if necessary, input to DR1 the

same signal as one input to DR0. Connect output DL0 to

DR0, and the output DL1 to DR1, of the next-stage IC.

For scanning signal transfer to the next-stage IC, see the

sections on the various functions.

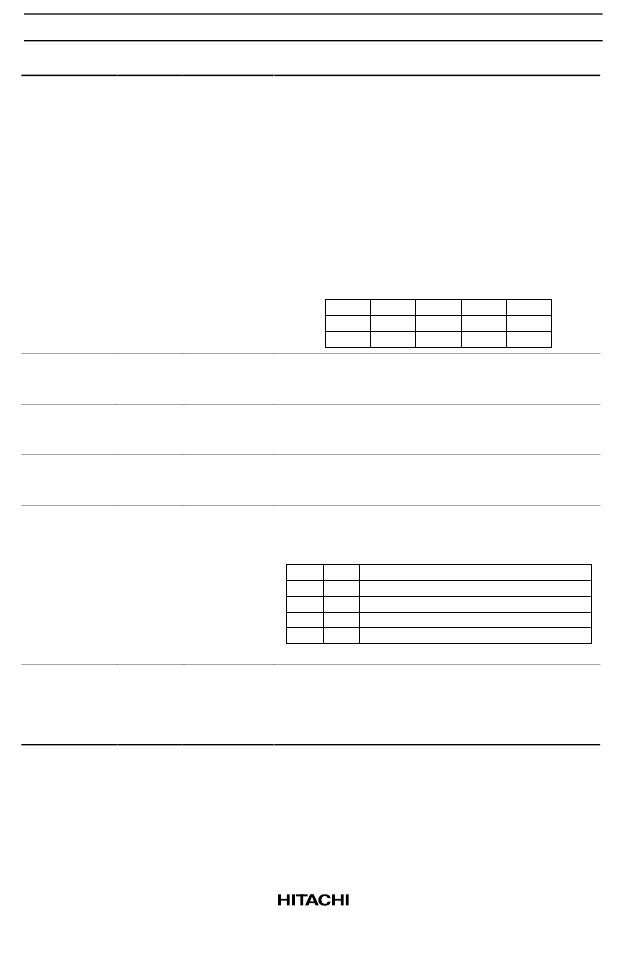

SHL

0

1

DL0

Input

Output

DL1

Input

Output

DR0

Output

Input

DR1

Output

Input

SHL

1

Input

Controls output scanning direction.

When SHL = 0, shift is performed in X1 to X257 direction.

When SHL = 1, shift is performed in X256 to X0 direction.

M

1

Input

The high or low level of this signal selects VM or VL from the

gate off-levels. If gate off-level alternation is not necessary,

fix this signal at low.

DISPOFF

1

Input

When this signal is driven low, all X pins output the VM level

regardless of the shift register contents or the M signal.

Shift register contents and operation are not affected.

FS0

FS1

2

Input

Gate line drive waveforms are generated for various drive

systems according to the settings of these signals.

For details, see the waveform examples (p. 8).

Drive System

Gate-coupling drive

Interlaced drive

Dot inversion/counter-electrode inversion drive

Dot inversion/counter-electrode inversion drive

FS0

0

1

0

1

FS1

0

0

1

1

FRM/LIN

1

Input

Valid when gate coupling drive is used; selects frame

alternation when high, line alternation when low.

With other drive waveforms, this signal is used at the low

level. In this case, gate off-level VM or VL is output

according to the M signal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HD66322T | 64-level Gray Scale Driver for High-Quality TFT Liquid Crystal Display for XGA and SXGA(TFT LCD的64級灰度驅(qū)動器) |

| HD66323 | 64-level Grayscale Driver for the TFT Liquid Crystal Display for XGA Systems(高品質(zhì)TFT LCD的64級灰度驅(qū)動器) |

| HD66324SA | 64-level Grayscale Driver for the High-Quality TFT Liquid Crystal Display for XGA/SXGA Systems(高品質(zhì)TFT LCD的64級灰度驅(qū)動器) |

| HD66324T | 64-level Grayscale Driver for the High-Quality TFT Liquid Crystal Display for XGA/SXGA Systems(高品質(zhì)TFT LCD的64級灰度驅(qū)動器) |

| HD66325A | 64-level Grayscale Driver for the TFT Liquid Crystal Display for XGA Systems(高品質(zhì)TFT LCD的64級灰度驅(qū)動器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HD66322T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| HD66324T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| HD66326T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| HD66330T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

| HD66330TA0 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD Display Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。