- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370686 > HS1-82C37ARH-8 (Harris Corporation) Radiation Hardened CMOS High Performance Programmable DMA Controller PDF資料下載

參數(shù)資料

| 型號: | HS1-82C37ARH-8 |

| 廠商: | Harris Corporation |

| 英文描述: | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| 中文描述: | 輻射加固的CMOS高性能可編程DMA控制器 |

| 文件頁數(shù): | 24/28頁 |

| 文件大?。?/td> | 253K |

| 代理商: | HS1-82C37ARH-8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁

24

HS-82C37ARH

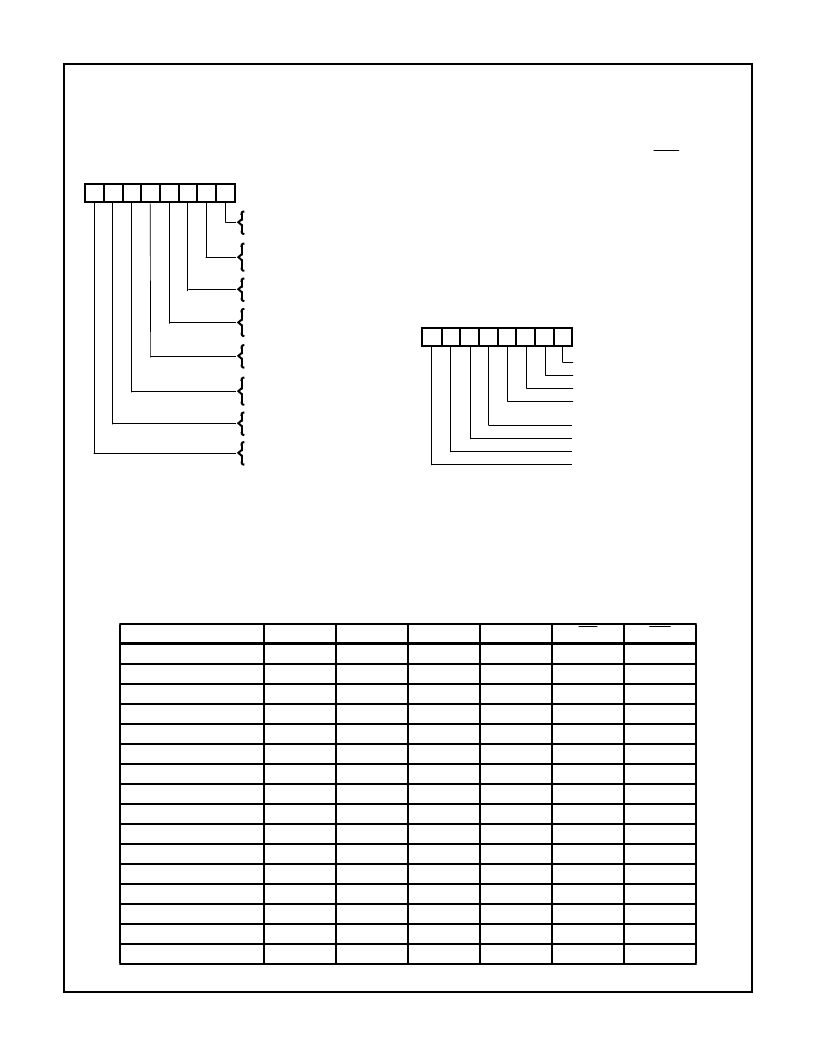

Command Register

- This 8-bit register controls the

operation of the HS-82C37ARH. It is programmed by the

microprocessor and is cleared by Reset or a Master Clear

instruction. The adjacent table lists the function of the

command bits. See Figure 10 for Read and Write addresses.

Command Registe

r

7

6

5

4

3

2

1

0

0

1

0

1

X

BIT NUMBER

MEM-TO-MEM DISABLE

MEM-TO-MEM ENABLE

CH. 0 ADDR. HOLD DISABLE

CH. 0 ADDR. HOLD ENABLE

IF BIT 0 = 0

0

1

CONTROLLER ENABLE

CONTROLLER DISABLE

0

1

X

NORMAL TIMING

COMPRESSED TIMING

IF BIT 0 = 1

0

1

FIXED PRIORITY

ROTATING PRIORITY

0

1

X

LATE WRITE SELECTION

EXTENDED WRITE SEL.

IF BIT 3 = 1

0

1

DREQ SENSE ACTIVE HIGH

DREQ SENSE ACTIVE LOW

0

1

DACK SENSE ACTIVE LOW

DACK SENSE ACTIVE HIGH

Status Register

- The Status Register contains information

about the present status of the HS-82C37ARH and can be

read by the microprocessor. This information includes which

channels have reached a terminal count and which channels

have pending DMA requests. Bits 0-3 are set every time a

TC is reached by that channel or an external EOP is applied.

These bits are cleared upon Reset, Master Clear, and on

each Status Read. Bits 4-7 are set whenever their corre-

sponding channel is requesting service, regardless of the

mask bit state. If the mask bits are set, software can poll the

Status Register to determine which channels have DREQs,

and selectively clear a mask bit, thus allowing user defined

service priority. Status bits 4-7 are updated while the clock is

high, and latched on the falling edge. Status Bits 4-7 are

cleared upon Reset or Master Clear.

Status Registe

r

Temporary Register

- The Temporary Register is used to

hold data during Memory-to-Memory transfers. Following the

completion of the transfer, the last word moved can be read

by the microprocessor by accessing this register. The Tem-

porary Register always contains the last byte transferred in

the previous Memory-to-Memory operation, unless cleared

by a Reset or Master Clear.

7

6

5

4

3

2

1

0

1

1

1

1

1

1

1

1

BIT NUMBER

CHANNEL 0 HAS REACHED TC

CHANNEL 1 HAS REACHED TC

CHANNEL 2 HAS REACHED TC

CHANNEL 3 HAS REACHED TC

CHANNEL 0 REQUEST

CHANNEL 1 REQUEST

CHANNEL 2 REQUEST

CHANNEL 3 REQUEST

OPERATION

A3

A2

A1

A0

IOR

IOW

Read Status Register

1

0

0

0

0

1

Write Command Register

1

0

0

0

1

0

Read Request Register

1

0

0

1

0

1

Write Request Register

1

0

0

1

1

0

Read Command Register

1

0

1

0

0

1

Write Single Mask Bit

1

0

1

0

1

0

Read Mode Register

1

0

1

1

0

1

Write Mode Register

1

0

1

1

1

0

Set Byte Pointer F/F

1

1

0

0

0

1

Clear Byte Pointer F/F

1

1

0

0

1

0

Read Temporary Register

1

1

0

1

0

1

Master Clear

1

1

0

1

1

0

Clear Mode Reg. Counter

1

1

1

0

0

1

Clear Mask Register

1

1

1

0

1

0

Read All Mask Bits

1

1

1

1

0

1

Write All Mask Bits

1

1

1

1

1

0

FIGURE 10. SOFTWARE COMMAND CODES AND REGISTER CODES

Spec Number

518058

相關PDF資料 |

PDF描述 |

|---|---|

| HS9-82C37ARH-8 | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS1-82C37ARH-Q | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS-82C12 | Radiation Hardened 8-Bit Input/Output Port |

| HS-82C12RH | Radiation Hardened 8-Bit Input/Output Port |

| HS1-82C37ARH | Radiation Hardened CMOS High Performance Programmable DMA Controller |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HS1-82C37ARH-Q | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS1-82C37ARH-SAMPLE | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS1-82C52RH-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UART |

| HS1-82C54RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Programmable Interval Timer |

| HS1-82C54RH/PROTO | 制造商:Intersil Corporation 功能描述:RAD HARD CMOS PROGRAMMABLE INTERVAL TIMER,PROTO,CLASS V - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。