- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370686 > HS9-82C37ARH-8 (Harris Corporation) Radiation Hardened CMOS High Performance Programmable DMA Controller PDF資料下載

參數(shù)資料

| 型號: | HS9-82C37ARH-8 |

| 廠商: | Harris Corporation |

| 英文描述: | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| 中文描述: | 輻射加固的CMOS高性能可編程DMA控制器 |

| 文件頁數(shù): | 21/28頁 |

| 文件大小: | 253K |

| 代理商: | HS9-82C37ARH-8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

21

HS-82C37ARH

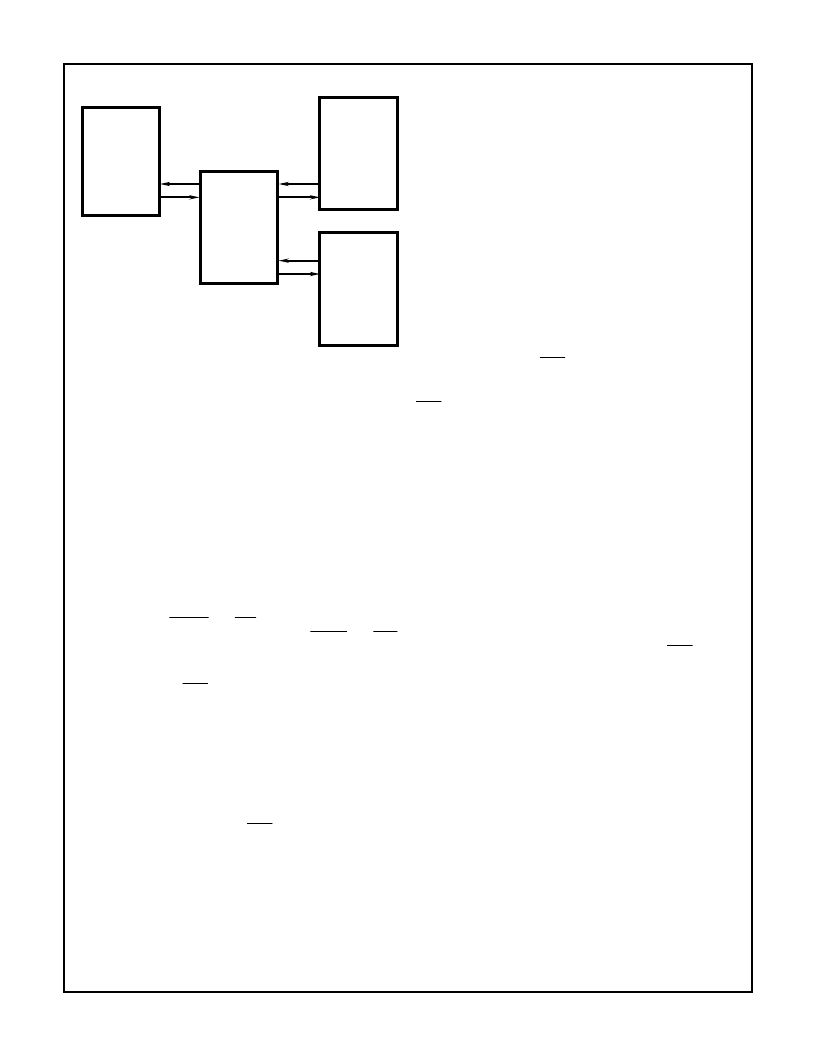

FIGURE 9. CASCADED HS-82C37ARHs

When programming cascaded controllers, start with the first

level (closest to the microprocessor). After RESET, the

DACK outputs are programmed to be active low and are

held in the high state. If they are used to drive HLDA directly,

the second level device(s) cannot be programmed until

DACK polarity is selected as active high on the initial device.

Also, the initial device’s mask bits function normally on cas-

caded channels, so they may be used to inhibit second-level

services.

Transfer Types

Each of the three active transfer modes can perform three

different types of transfers. These are Read, Write and Ver-

ify. Write transfers move data from an I/O device to the mem-

ory by activating MEMW and IOR. Read transfers move data

from memory to an I/O device by activating MEMR and IOW.

Verify transfers are pseudo-transfers. The HS-82C37ARH

operates as in Read or Write transfers generating addresses

and responding to EOP, etc., however the memory and I/O

control lines all remain inactive. Verify mode is not permitted

for Memory-to-Memory operation. Ready is ignored during

Verify transfers.

Autoinitialize

- By programming a bit in the Mode Register,

a channel may be set up as an Autoinitialize channel. During

Autoinitialization, the original values of the Current Address

and Current Word Count Registers are automatically

restored from the Base Address and Base Word Count Reg-

isters of that channel following EOP. The base registers are

loaded simultaneously with the current registers by the

microprocessor and remain unchanged throughout the DMA

service. The mask bit is not set when the channel is in Auto-

initialize. Following Autoinitialization, the channel is ready to

perform another DMA service, without CPU intervention, as

soon as a valid DREQ is detected, or software request made.

Memory-to-Memory

- To perform block moves of data from

one memory address space to another with minimum of pro-

HS-80C86RH

MICRO-

PROCESSOR

1ST LEVEL

HRQ

HLDA

DREQ

DACK

HS-82C37ARH

DREQ

DACK

INITIAL DEVICE

2ND LEVEL

HRQ

HLDA

HS-82C37ARH

HRQ

HLDA

HS-82C37ARH

ADDITIONAL

DEVICES

gram effort and time, the HS-82C37ARH includes a Mem-

ory-to-Memory transfer feature. Programming a bit in the

Command Register selects channels 0 and 1 to operate as

Memory-to-Memory transfer channels.

The transfer is initiated by setting the software or hardware

DREQ for channel 0. The HS-82C37ARH requests a DMA

service in the normal manner. After HLDA is true, the device,

using four-state transfers in Block Transfer Mode, reads data

from the memory. The channel 0 Current Address Register is

the source for the address used and is decremented or

incremented in the normal manner. The data byte read from

the memory is stored in the HS-82C37ARH internal Tempo-

rary Register. Another four-state transfer moves the data to

memory using the address in channel 1’s Current Address

Register and incrementing or decrementing it in the normal

manner. The channel 1 Current Word Count Register is dec-

remented.

When the word count of channel 1 goes to FFFFH, a TC is

generated causing an EOP output terminating the service.

Channel 0 word count decrementing to FFFFH will not set

the channel 0 TC bit in the Status Register or generate an

EOP in this mode. It will cause an Autoinitialization of chan-

nel 0, if that option has been selected.

If full Autoinitialization for a Memory-to-Memory operation is

desired, the channel 0 and channel 1 word counts must be

set equal before the transfer begins. Otherwise, if channel 0

underflows before channel 1, it will Autoinitialize and set the

data source address back to the beginning of the block. If

the channel 1 word count underflows before channel 0, the

Memory-to-Memory DMA service will terminate, and channel

1 will Autoinitialize but channel 0 will not.

In Memory-to-Memory Mode, Channel 0 may be pro-

grammed to retain the same address for all transfers. This

allows a single byte to be written to a block of memory. This

channel 0 address hold feature is selected by bit 1 in the

Command Register.

The HS-82C37ARH will respond to external EOP signals

during Memory-to-Memory transfers, but will only relinquish

the system busses after the transfer is complete (i.e., after

an S24 state). Data comparators in block search schemes

may use this input to terminate the service when a match is

found. The timing of Memory-to-Memory transfers is found in

Figure 5. Memory-to-Memory operations can be detected as

an active AEN with no DACK outputs.

Priority

- The HS-82C37ARH has two types of priority

encoding available as software selectable options. The first

is Fixed Priority which fixes the channels in priority order

based upon the descending value of their numbers. The

channel with the lowest priority is 3 followed by 2, 1 and the

highest priority channel, 0. After the recognition of any one

channel for service, the other channels are prevented from

interfering with the service until it is completed.

The second scheme is Rotating Priority. The last channel to

get service becomes the lowest priority channel with the oth-

ers rotating accordingly. The next lower channel from the

channel serviced has highest priority on the following

request: Priority rotates every time control of the system

busses is returned to the processor.

Spec Number

518058

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS1-82C37ARH-Q | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS-82C12 | Radiation Hardened 8-Bit Input/Output Port |

| HS-82C12RH | Radiation Hardened 8-Bit Input/Output Port |

| HS1-82C37ARH | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C37ARH-Q | Radiation Hardened CMOS High Performance Programmable DMA Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS9-82C37ARH-Q | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C54RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Programmable Interval Timer |

| HS9-82C54RH-8 | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24PIN CFLATPACK - Bulk |

| HS9-82C54RH-Q | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24CFPAK - Bulk |

| HS9-82C85RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Static Clock Controller/Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。