- 您現在的位置:買賣IC網 > PDF目錄371896 > HSP43216VC-52 (INTERSIL CORP) Halfband Filter PDF資料下載

參數資料

| 型號: | HSP43216VC-52 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 數字信號處理外設 |

| 英文描述: | Halfband Filter |

| 中文描述: | 16-BIT, DSP-DIGITAL FILTER, PQFP100 |

| 封裝: | 14 X 20 MM, PLASTIC, MS-022GC, MQFP-100 |

| 文件頁數: | 14/19頁 |

| 文件大小: | 144K |

| 代理商: | HSP43216VC-52 |

3-206

If external multiplexing is selected (INT/EXT = 0), a

demultiplex function is required off chip to break the input data

stream into even and odd samples for input through AIN0-15

and BIN0-15. In this mode, the real and imaginary processing

legs run at the input clock rate which allows the device to

perform the down convert and decimate function on real

signals sampled at up to twice the maximum speed grade of

the device (104 MSPS). With external multiplexing, the

minimum pipeline delay through the upper processing leg is 9

CLK’s and the pipeline delay through the lower processing leg

is 26 CLK’s as shown in Figure 15B. To synchronize the even

samples input through AIN0-15 with the zero degree cosine

term of the quadrature LO, SYNC should be asserted on the

same clock that the target sample is present at the input of the

part as shown in Figure 17.

NOTE: For proper operation,

the samples demultiplexed to the AIN0-15 input must

precede those input to the BIN0-15 input in sample order.

For example, given a data sequence x0, x1, x2, and x3,

the demultiplex function would route x0 and x2 to AIN0-

15 and x1 and x3 to BIN0-15.

Quadrature to Real Conversion Mode (MODE1-0 = 11)

The Quadrature to Real Conversion mode is used to

construct a real output from a quadrature input. To

accomplish this, the Halfband Filter Processor interpolates

the quadrature components of the complex input signal by

a factor of two. Next, the Quadrature Up-Convert Processor

spectrally shifts the signal by f

S

/4 and derives the real

output as described in the f

S

/4 Quadrature Up-Convert

Processor Section. The direction of the spectral shift is

controlled via the USB/LSB input and is used to designate

the frequency content of the complex input as either the

upper or lower sideband of the resulting real output signal.

A spectral representation of quadrature to real conversion

is shown in Figure 18 for USB/LSB = 1.

NOTE: The f

S

/4

Up-Convert Processor uses quadrature mix factors

scaled by two to compensate for the attenuation

introduced by the interpolation process.

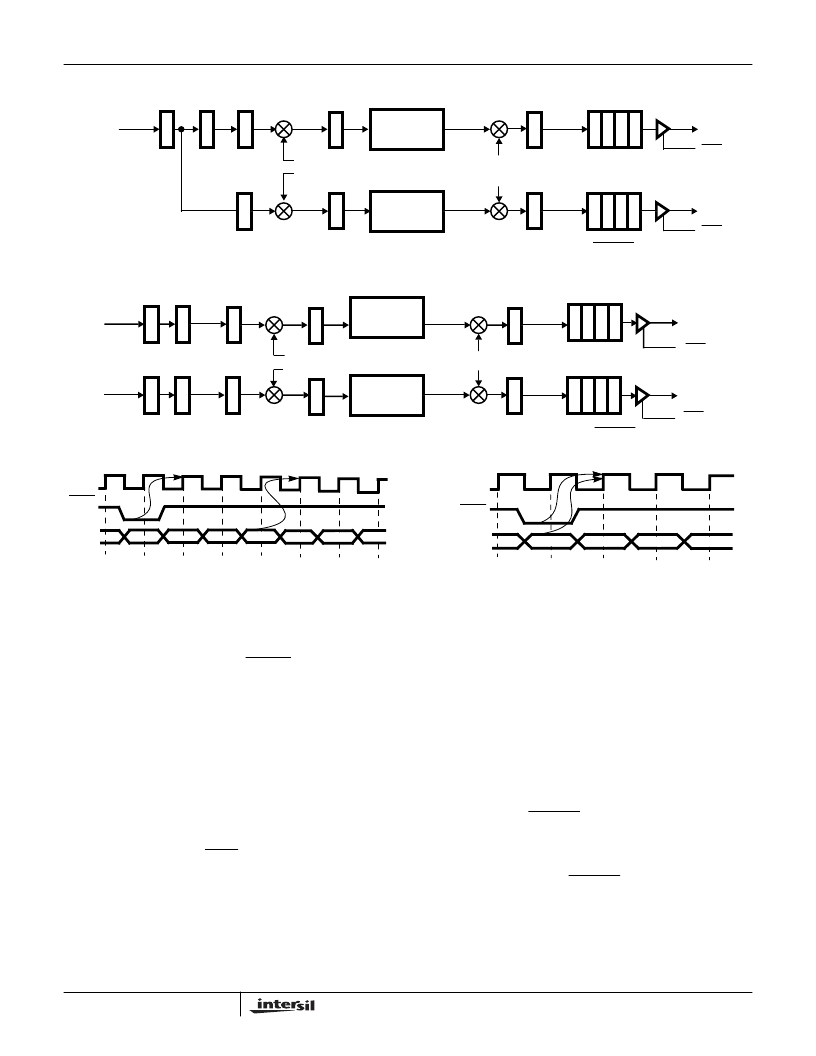

FIGURE 15A. DATA FLOW DIAGRAM FOR DOWN CONVERT AND DECIMATE MODE (INT/EXT = 1)

FIGURE 15B. DATA FLOW DIAGRAM FOR DOWN CONVERT AND DECIMATE MODE (INT/EXT = 0)

EVEN TAP

FILTER

ODD TAP

FILTER

AIN0-15

AOUT0-15

OEA

R

E

G

R

E

G

R

E

G

R

E

G

R

E

G

R

E

G

R

N

D

F

M

T

R

E

G

R

E

G

R

E

G

R

E

G

1,-1,1,-1,...

-1,1,-1,1,...

2

2

BOUT0-15

OEB

R

N

D

F

M

T

R

E

G

R

E

G

Clocked at CLK/2

GROUP DELAY 19

PIPELINE DELAY 2-35

GROUP DELAY 19

PIPELINE DELAY 19

EVEN TAP

FILTER

ODD TAP

FILTER

AIN0-15

AOUT0-15

OEA

R

E

G

R

E

G

R

E

G

R

E

G

R

E

G

R

E

G

R

N

D

F

M

T

R

E

G

R

E

G

R

E

G

R

E

G

1,-1,1,-1,...

-1,1,-1,1,...

2

2

BOUT0-15

OEB

R

N

D

F

M

T

R

E

G

R

E

G

BIN0-15

R

E

G

R

E

G

GROUP DELAY 19

PIPELINE DELAY 2-35

GROUP DELAY 19

PIPELINE DELAY 19

0

1

2

CLK

SYNC

AIN0-15

3

THE SAMPLE DESIGNATED BY THE 0

o

AND 180

o

LABELS ARE MIXED

WITH THE RESPECTIVE COSINE TERMS ON THE UPPER PROCESSING

LEG, AND THE OTHER SAMPLES, THOSE LABELED BY 90

o

AND 270

o

,

ARE MIXED WITH THE RESPECTIVE SINE TERMS ON THE LOWER LEG.

FIGURE 16. DATA SYNCHRONIZATION TO 0

o

PHASE OF

QUADRATURE LO

0

o

90

o

180

o

270

o

0

1

2

CLK

SYNC

AIN0-15

THE 0

o

AND 180

o

LABELS INDICATE THE PHASE ALIGNMENT OF

THE SAMPLES INPUT THROUGH AIN0-15 WITH THE COSINE TERM

OF THE QUADRATURE DOWN CONVERT LO.

FIGURE 17. DATA SYNCHRONIZATION WITH PHASE OF

DOWN CONVERT LO

0

o

180

o

180

o

0

o

HSP43216

相關PDF資料 |

PDF描述 |

|---|---|

| HSP43216 | Halfband Filter |

| HSP43216JC-52 | Halfband Filter |

| HSP43220JC-15 | Circular Connector; MIL SPEC:MIL-C-5015; Body Material:Metal; Series:GT; No. of Contacts:4; Connector Shell Size:24; Connecting Termination:Solder; Circular Shell Style:Box Mount Receptacle; Body Style:Straight |

| HSP43220GC-25 | Decimating Digital Filter |

| HSP43220GC-33 | Decimating Digital Filter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HSP43216VC-52Z | 功能描述:有源濾波器 W/ANNEAL HALFB & FILER 100 PIN PQFP RoHS:否 制造商:Maxim Integrated 通道數量:1 截止頻率:150 KHz 電源電壓-最大:11 V 電源電壓-最小:4.74 V 最大工作溫度:+ 85 C 安裝風格:Through Hole 封裝 / 箱體:PDIP N 封裝:Tube |

| HSP43220 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220/883 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220_04 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

| HSP43220883 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Decimating Digital Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復。