- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370804 > HYS64V4220GU-10 (SIEMENS A G) 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module PDF資料下載

參數(shù)資料

| 型號(hào): | HYS64V4220GU-10 |

| 廠商: | SIEMENS A G |

| 元件分類(lèi): | DRAM |

| 英文描述: | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| 中文描述: | 4M X 64 SYNCHRONOUS DRAM MODULE, 8 ns, DMA168 |

| 封裝: | DIMM-168 |

| 文件頁(yè)數(shù): | 10/17頁(yè) |

| 文件大?。?/td> | 104K |

| 代理商: | HYS64V4220GU-10 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

HYS64(72)V2200/4220GU-8/-10

SDRAM-Modules

Semiconductor Group

10

Notes:

1. The specified values are valid when addresses are changed no more than once during tck(min.)

and when No Operation commands are registered on every rising clock edge during tRC(min).

Values are shown per module bank.

2. The specified values are valid when data inputs (DQ’) are stable during tRC(min.).

3. All AC characteristics are shown for device level.

An initial pause of 100

μ

s is required after power-up, then a Precharge All Banks command must

be given followed by 8 Auto Refresh (CBR) cycles before the Mode Register Set Operation can

begin.

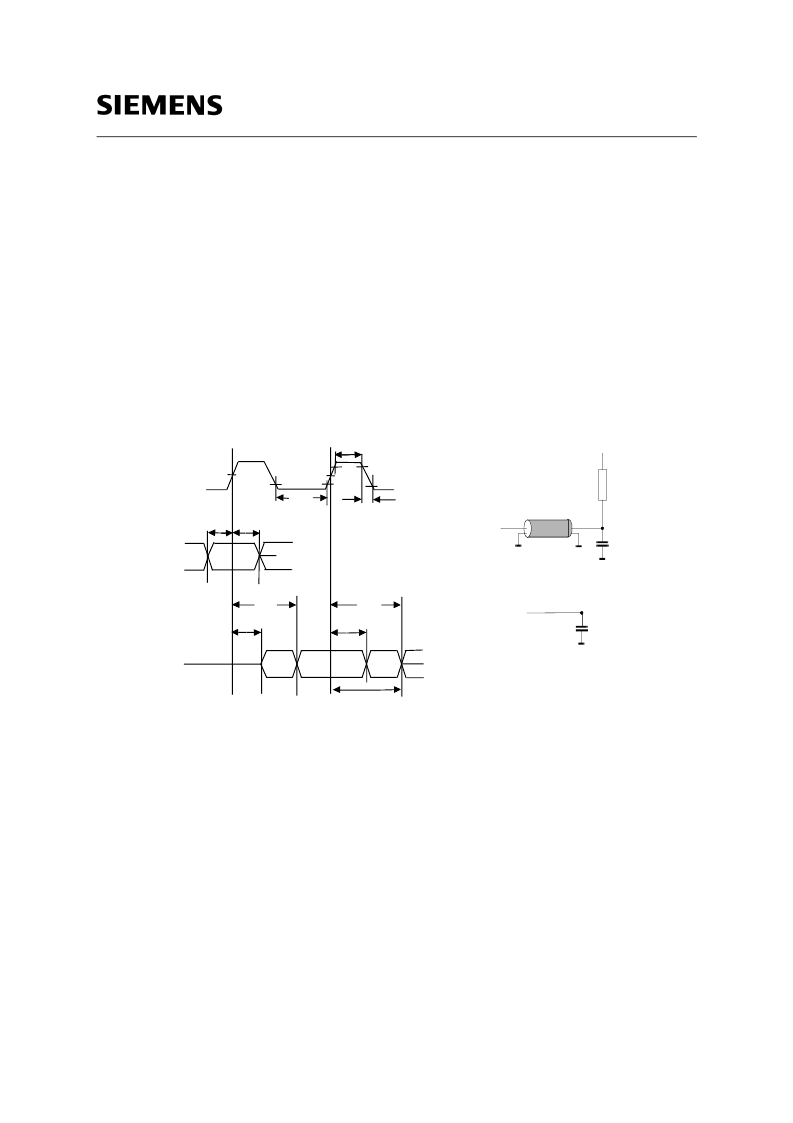

4. AC timing tests have V

il

= 0.4 V and V

ih

= 2.4 V with the timing referenced to the 1.4 V crossover

point. The transition time is measured between V

ih

and V

il

. All AC measurements assume t

T

=1ns

with the AC output load circuit show. Specified tac and toh parameters are measured with a 50

pF only, without any resistive termination and with a input signal of 1V / ns edge rate between

0.8V and 2.0 V.

tCH

5. If clock rising time is longer than 1ns, a time (t

T

/2 -0.5) ns has to be added to this parameter.

6. Rated at 1.5 V

7. If t

T

is longen than 1 ns, a time (t

T

-1) ns has to be added to this parameter.

8. Any time that the refresh Period has been exceeded, a minimum of two Auto (CBR) Refresh

commands must be given to “wake-up“the device.

9. Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after

CKE returns high. Self Refresh Exit is not complete until a time period equal to tRC is satisfied

once the Self Refresh Exit command is registered.

10.Referenced to the time which the output achieves the open circuit condition, not to output voltage

levels.

11.t

DAL

is equivalent to t

DPL

+ t

RP

.

1.4V

1.4V

tSETUP

tHOLD

tAC

tAC

tLZ

tOH

tHZ

CLOCK

INPUT

OUTPUT

50 pF

I/O

Z=50 Ohm

+ 1.4 V

50 Ohm

2.4 V

0.4 V

t

T

fig.1

tCL

50 pF

I/O

Measurement conditions for

tac and toh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72V4220GU-10 | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V4220GU-8 | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V4220GU-8-3 | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V2200GU-8-3 | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS72V2200GU-8-3 | 3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS64V4220GU-8 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V4220GU-8-3 | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:3.3V 2M x 64/72-Bit 1 BANK SDRAM Module 3.3V 4M x 64/72-Bit 2 BANK SDRAM Module |

| HYS64V4300GU-10 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:x64 SDRAM Module |

| HYS64V4300GU-7.5 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:x64 SDRAM Module |

| HYS64V64220GBDL | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:144 pin SO-DIMM SDRAM Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。