- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377412 > IDT72261L15PFB (INTEGRATED DEVICE TECHNOLOGY INC) CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72261L15PFB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

| 中文描述: | 16K X 9 OTHER FIFO, PQFP64 |

| 封裝: | TQFP-64 |

| 文件頁數(shù): | 28/30頁 |

| 文件大?。?/td> | 388K |

| 代理商: | IDT72261L15PFB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁

28

MILITARY AND COMMERCIAL TEMPERATURE RANGES

IDT72261/72271 SyncFIFO

16,384 x 9, 32,768 x 9

OPERATING CONFIGURATIONS

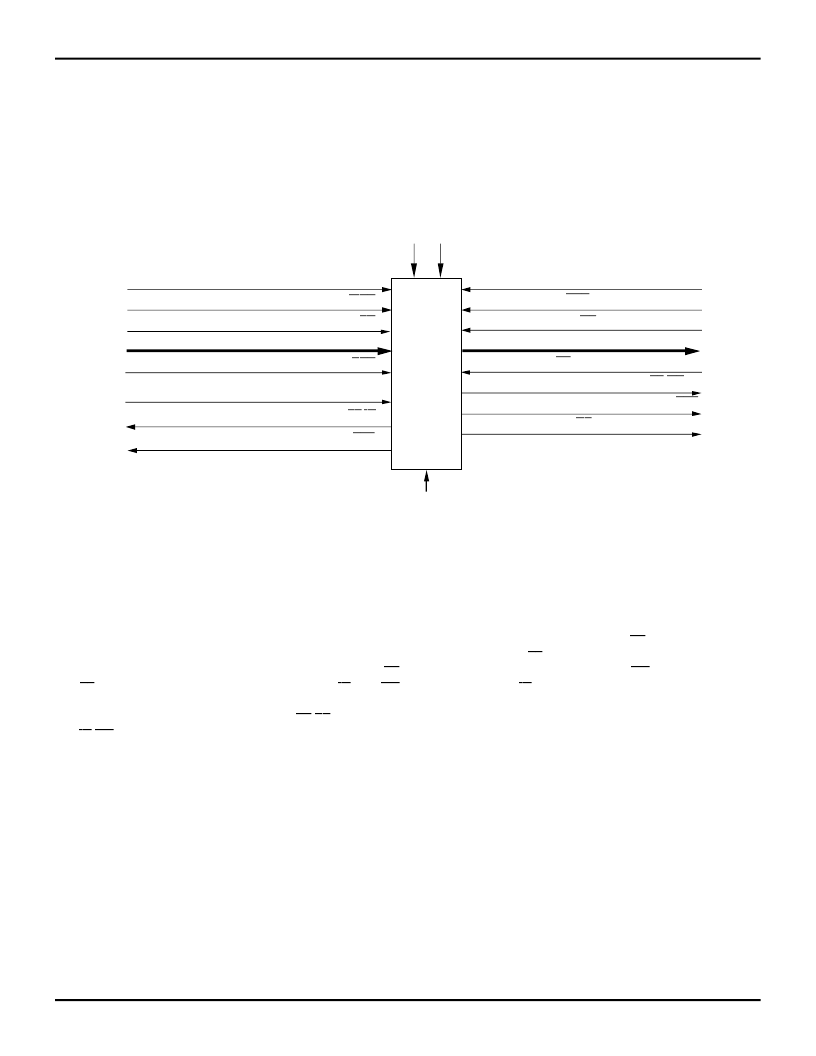

SINGLE DEVICE CONFIGURATION

A single IDT72261/722171 may be used when the applica-

tion requirements are for 16,384/32,768 words or less. The

IDT72261/72271 can always be used in Single Device Con-

figuration, whether IDT Standard Mode or FWFT Mode has

been selected. No special set up procedure is necessary.

Figure 21. Block Diagram of Single 16,384x9/32,768x9 Synchronous FIFO

WIDTH EXPANSION CONFIGURATION

Word width may be increased simply by connecting to-

gether the control signals of multiple devices. Status flags can

be detected from any one device. The exceptions are the

EF

and

FF

functions in IDT Standard mode and the

IR

and

OR

functions in FWFT mode. Because of variations in skew

between RCLK and WCLK, it is possible for

EF

/

FF

deassertion

and

IR

/

OR

assertion to vary by one cycle between FIFOs. In

IDT Standard mode, such problems can be avoided by creat-

ing composite flags, that is, ANDing

EF

of every FIFO, and

separately ANDing

FF

of every FIFO. In FWFT mode, com-

posite flags can be created by ORing

OR

of every FIFO, and

separately ORing

IR

of every FIFO. Figure 22 demonstrates

an 18-word width by using two IDT72261/72271s. Any word

width can be attained by adding additional IDT7226172271s.

DATA OUT (Q

0

- Q

8

)

DATA IN (D

0

- D

8

)

MASTER RESET (

MRS

)

READ CLOCK (RCLK)

READ ENABLE (

REN

)

OUTPUT ENABLE (

OE

)

EMPTY FLAG/OUTPUT READY (

EF

/

OR

)

PROGRAMMABLE ALMOST EMPTY (

PAE

)

WRITE CLOCK (WCLK)

WRITE ENABLE (

WEN

)

LOAD (

LD

)

FULL FLAG/INPUT READY (

FF

/

IR

)

PROGRAMMABLE ALMOST FULL (

PAF

)

IDT

72261/

72271

PARTIAL RESET (

PRS

)

FIRST WORD FALL THROUGH/SERIAL INPUT

(FWFT/SI)

RETRANSMIT (

RT

)

3036 drw 24

HALF FULL FLAG (

HF

)

FREQUENCY SELECT (FS)

SERIAL ENABLE(

SEN

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72261L15TF | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

| IDT72261L15TFB | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

| IDT72261L20G | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

| IDT72261L20GB | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

| IDT72261L20PF | CMOS SUPERSYNC FIFOO 16,384 x 9, 32,768 x 9 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72261LA10PF | 功能描述:IC FIFO 8192X18 LP 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA10PF8 | 功能描述:IC FIFO 8192X18 LP 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA10TF | 功能描述:IC FIFO 8192X18 LP 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA10TF8 | 功能描述:IC FIFO 8192X18 LP 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72261LA15PF | 功能描述:IC FIFO 8192X18 LP 15NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。