- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67716 > IDT79RV4650133DPG (INTEGRATED DEVICE TECHNOLOGY INC) 64-BIT, 133 MHz, RISC PROCESSOR, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | IDT79RV4650133DPG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 133 MHz, RISC PROCESSOR, PQFP208 |

| 封裝: | 28 X 28 MM, 3.40 MM HEIGHT, PLASTIC, QFP-208 |

| 文件頁數(shù): | 25/25頁 |

| 文件大?。?/td> | 660K |

| 代理商: | IDT79RV4650133DPG |

9 of 25

April 10, 2001

IDT79RC4650

The following is a list of the supported external requests:

◆

Read Response

◆

Null

Boot-Time Options

Fundamental operational modes for the processor are initialized by

the boot-time mode control interface. The boot-time mode control inter-

face is a serial interface operating at a very low frequency (MasterClock

divided by 256). The low-frequency operation allows the initialization

information to be kept in a low-cost EPROM; alternatively the twenty-or-

so bits could be generated by the system interface ASIC or a simple

PAL.

To initialize all fundamental, operational modes, immediately after the

VCCOK signal is asserted, the processor reads a serial bit stream of 256

bits. After initialization is complete, the processor continues to drive the

serial clock output, but no further initialization bits are read.

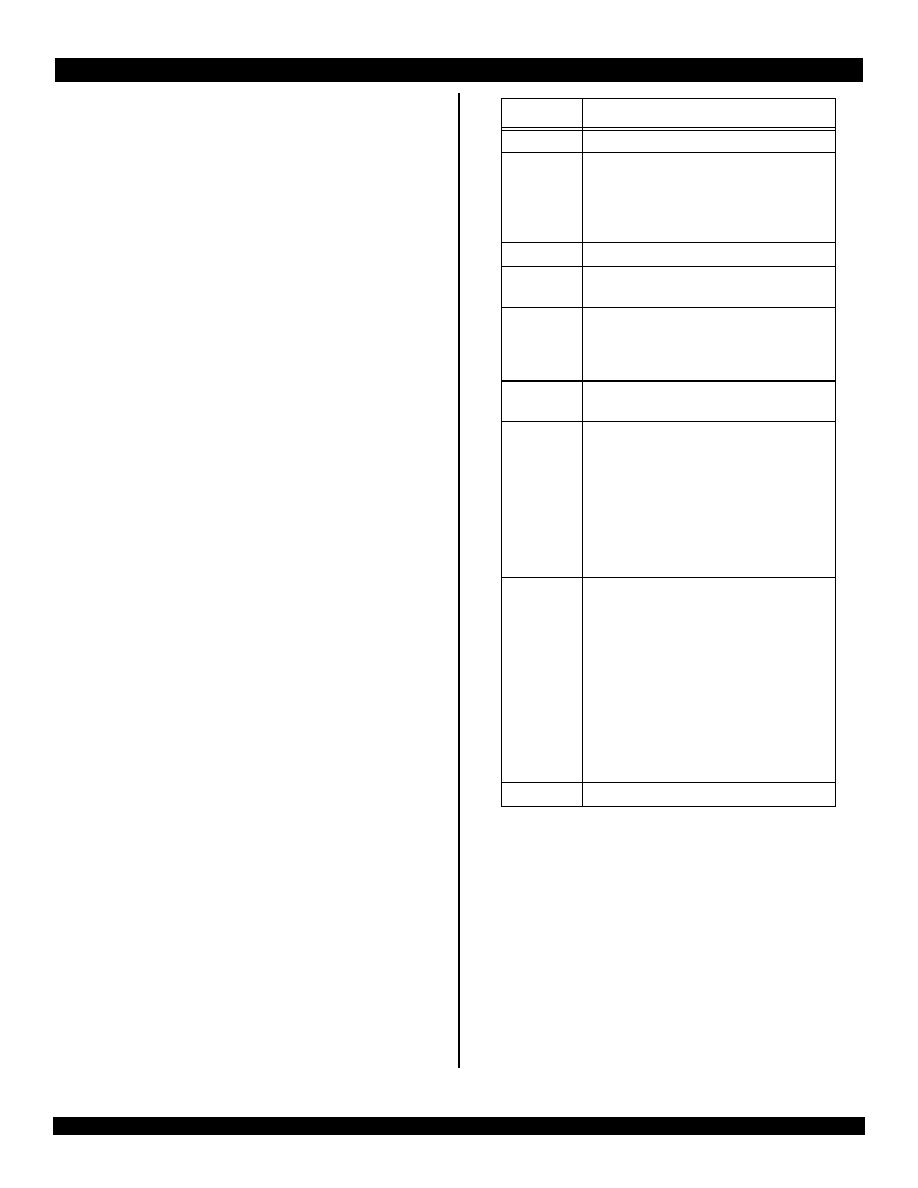

Boot-Time Modes

The boot-time serial mode stream is defined in Table 5. Bit 0 is the bit

presented to the processor when VCCOK is asserted; bit 255 is the last.

Power Management

CP0 is also used to control the power management for the RC4650.

This is the standby mode and it can be used to reduce the power

consumption of the internal core of the CPU. The standby mode is

entered by executing the WAIT instruction with the SysAD bus idle and

is exited by any interrupt.

Standby Mode Operation

The RC4650 provides a means to reduce the amount of power

consumed by the internal core when the CPU would otherwise not be

performing any useful operations. This is known as “Standby Mode.”

Entering Standby Mode

Executing the WAIT instruction enables interrupts and enters

Standby mode. When the WAIT instruction finishes the W pipe-stage, if

the SysAd bus is currently idle, the internal clocks will shut down, thus

freezing the pipeline. The PLL, internal timer, and some of the input pins

(Int[5:0]*, NMI*, ExtReq*, Reset*, and ColdReset*) will continue to run. If

the conditions are not correct when the WAIT instruction finishes the W

pipe-stage (i.e. the SysAd bus is not idle), the WAIT is treated as a NOP.

Once the CPU is in Standby Mode, any interrupt, including the inter-

nally generated timer interrupt, will cause the CPU to exit Standby

Mode.

Thermal Considerations

The RC4650 utilizes special packaging techniques to improve the

thermal properties of high-speed processors. The RC4650 is packaged

using cavity down packaging in a 208-pin QFP (DP). The QFP package

allows for an efficient thermal transfer between the die and the case.

The R4650 and the RV4650 are guaranteed in a case temperature

range of 0

°C to +85°C for commercial temperature parts and in a case

temperature range of -40

°C to +85°C for industrial temperature parts.

The type of package, speed (power) of the device, and airflow conditions

affect the equivalent ambient temperature conditions that will meet this

specification. The equivalent allowable ambient temperature, TA, can be

Mode bit

Description

255..15

Must be zero

14..13

Output driver strength:

10

→ 100% strength (fastest)

11

→ 83% strength

00

→ 67% strength

01

→ 50% strength (slowest)

11

Disable the timer interrupt on Int[5]

12

0

→ 64-bit system interface

1

→ 32-bit system interface

10..9

00

→ RC4000 compatible

01

→ reserved

10

→ pipelined writes

11

→ write re-issue

80

→ Little endian

1

→ Big endian

7..5

Clock multiplier:

0

→ 2

1

→ 3

2

→ 4

3

→ 5

4

→ 6

5

→ 7

6

→ 8

7 reserved

4..1

Writeback data rate:

64-bit

0

→

1

→ DDx

2

→ DDxx

3

→ DxDx

4

→ DDxxx

5

→ DDxxxx

6

→ DxxDxx

7

→ DDxxxxxx

8

→ DxxxDxxx

9-15 reserved

32-bit

0

→

1

→ WWx

2

→ WWxx

3

→ WxWx

4

→ WWxxx

5

→ WWxxxx

6

→ WxxWxx

7

→ WWxxxxxx

8

→ WxxxWxxx

9-15 reserved

0

Reserved (must be zero)

Table 5 Boot-time mode stream

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT79RV4650180DPI | 64-BIT, 180 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4650180MS | 64-BIT, 180 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4650-133MS | 64-BIT, 133 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4650200MS | 64-BIT, 200 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4650100MSI | 64-BIT, 100 MHz, RISC PROCESSOR, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT79RV4650-150DP | 功能描述:IC MPU 64BIT W/DSP 150MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4650-180DP | 功能描述:IC MPU 64BIT W/DSP 180MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4650-200DP | 功能描述:IC MPU 64BIT W/DSP 200MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4650-267DP | 功能描述:IC MPU 64BIT W/DSP 267MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RV4700100DP | 制造商:Integrated Device Technology Inc 功能描述:64-BIT, 100 MHz, RISC PROCESSOR, PQFP208 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。