- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > INTEL486 SX (Intel Corp.) Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | INTEL486 SX |

| 廠商: | Intel Corp. |

| 英文描述: | Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) |

| 中文描述: | Emedded超低功耗英特爾486山西處理器(嵌入式超低能量處理器) |

| 文件頁數(shù): | 15/38頁 |

| 文件大小: | 346K |

| 代理商: | INTEL486 SX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

Embedded Ultra-Low Power Intel486 SX Processor

11

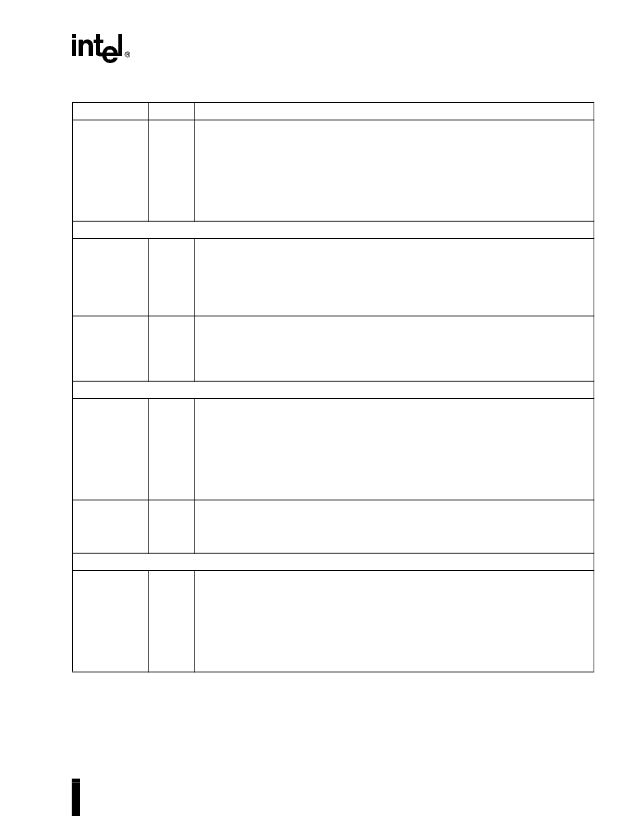

BOFF#

I

Backoff

nput forces the embedded ULP Intel486 SX processor to float its bus in

the next clock. The processor floats all pins normally floated during bus hold but

HLDA is not asserted in response to BOFF#. BOFF# has higher priority than RDY#

or BRDY#; if both are returned in the same clock, BOFF# takes effect. The

embedded ULP Intel486 SX processor remains in bus hold until BOFF# is

negated. If a bus cycle is in progress when BOFF# is asserted the cycle is

restarted. BOFF# is active LOW and must meet setup and hold times t

18

and t

19

for

proper operation.

CACHE INVALIDATION

AHOLD

I

Address Hold

request allows another bus master access to the embedded ULP

Intel486 SX processor

’s address bus for a cache invalidation cycle. The processor

stops driving its address bus in the clock following AHOLD going active. Only the

address bus is floated during address hold, the remainder of the bus remains

active. AHOLD is active HIGH and is provided with a small internal pull-down

resistor. For proper operation, AHOLD must meet setup and hold times t

18

and t

19

.

External Address

- This signal indicates that a

valid

external address has been

driven onto the embedded ULP Intel486 SX processor address pins. This address

is used to perform an internal cache invalidation cycle. EADS# is active LOW and

is provided with an internal pull-up resistor. EADS# must satisfy setup and hold

times t

12

and t

13

for proper operation.

EADS#

I

CACHE CONTROL

KEN#

I

Cache Enable

pin is used to determine whether the current cycle is cacheable.

When the embedded ULP Intel486 SX processor generates a cycle that can be

cached and KEN# is active one clock before RDY# or BRDY# during the first

transfer of the cycle, the cycle becomes a cache line fill cycle. Returning KEN#

active one clock before RDY# during the last read in the cache line fill causes the

line to be placed in the on-chip cache. KEN# is active LOW and is provided with a

small internal pull-up resistor. KEN# must satisfy setup and hold times t

14

and t

15

for proper operation.

Cache Flush

input forces the embedded ULP Intel486 SX processor to flush its

entire internal cache. FLUSH# is active LOW and need only be asserted for one

clock. FLUSH# is asynchronous but setup and hold times t

20

and t

21

must be met

for recognition in any specific clock.

FLUSH#

I

PAGE CACHEABILITY

PWT

PCD

O

O

Page Write-Through

and

Page Cache Disable

pins reflect the state of the page

attribute bits, PWT and PCD, in the page table entry, page directory entry or

control register 3 (CR3) when paging is enabled. When paging is disabled, the

embedded ULP Intel486 SX processor ignores the PCD and PWT bits and

assumes they are zero for the purpose of caching and driving PCD and PWT pins.

PWT and PCD have the same timing as the cycle definition pins (M/IO#, D/C#, and

W/R#). PWT and PCD are active HIGH and are not driven during bus hold. PCD is

masked by the cache disable bit (CD) in Control Register 0.

Table 4. Embedded ULP Intel486

SX Processor Pin Descriptions

(Sheet 5 of 6)

Symbol

Type

Name and Function

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INTEL82801 | 82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | Firmware Hub (FWH) |

| INTELDX2 | High-Performance 32-Bit Embedded Processor(高性能32位嵌入式處理器) |

| INTELDX4 | Embedded Write-Back Enhanced Processor(32位回復(fù)嵌入式增強(qiáng)型處理器) |

| IPS54511 | FULLY PROTECTED HIGH SIDE POWER MOSFET SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL740 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Graphics (GUI) Accelerator |

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

| INTELLI-INCH-LR-STARTER K | 制造商:ALL MOTION 功能描述:Intelli-Inch Stepper & Controller Starter Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。