- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > INTEL486 SX (Intel Corp.) Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) PDF資料下載

參數(shù)資料

| 型號: | INTEL486 SX |

| 廠商: | Intel Corp. |

| 英文描述: | Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) |

| 中文描述: | Emedded超低功耗英特爾486山西處理器(嵌入式超低能量處理器) |

| 文件頁數(shù): | 6/38頁 |

| 文件大小: | 346K |

| 代理商: | INTEL486 SX |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

2

Embedded Ultra-Low Power Intel486 SX Processor

Auto HALT Power Down —

After the execution of

a HALT instruction, the embedded ULP Intel486

SX processor issues a normal Halt bus cycle and

the clock input to the processor core is automati-

cally stopped, causing the processor to enter the

Auto HALT Power Down state (40–85 mW typical,

depending on input clock frequency).

The embedded ULP Intel486 SX processor differs

from the Intel486 SX processor in the following

areas:

Processor Upgrade Removed —

The UP# signal

is not provided.

Parity Signals Removed

— The DP3-DP0 and

PCHK# signals are not provided.

Separate Processor-Core Power

— While the

embedded ULP Intel486 SX processor requires a

supply voltage of 3.3 V, the processor core has

dedicated V

pins and operates with a supply

voltage as low as 2.4 V.

Small, Low-Profile Package

— The 176-Lead

Thin Quad Flat Pack (TQFP) package is approxi-

mately 26 mm square and only 1.5 mm in height.

This is approximately the diameter and thickness

of a U.S. quarter. The embedded ULP Intel486 SX

processor is ideal for embedded hand-held and

battery-powered applications.

Level Keeper Circuits

— The embedded ULP

Intel486 SX processor has level-keeper circuits for

its 32-bit external data bus signals. They retain

valid high and low logic voltage levels when the

processor is in the Stop Grant and Stop Clock

states. This is a power-saving improvement from

the floating data bus of the Intel486 SX processor.

Auto Clock Freeze

— The embedded ULP

Intel486 SX processor monitors bus events and

internal activity. The Auto Clock Freeze feature

automatically controls internal clock distribution,

turning off clocks to internal units when they are

idle. This power-saving function is transparent to

the embedded system.

Fast Clock Restart

— The embedded ULP

Intel486 SX processor requires only eight clock

periods to synchronize its internal clock with the

CLK input signal. This provides for faster transition

from the Stop Clock State to the Normal State. For

33-MHz operation, this synchronization time is

only 240 ns compared with 1 ms (PLL startup

latency) for the Intel486 processor.

1.2

Family Members

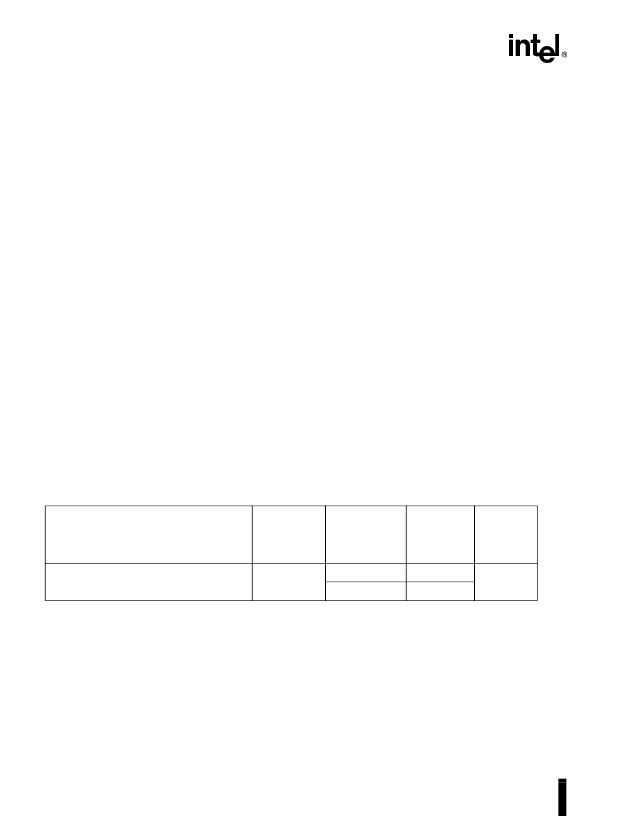

Table 1 shows the embedded ULP Intel486 SX

processor and briefly describes its characteristics.

Table 1. The Embedded Ultra-Low Power Intel486

SX Processor

Product

Supply

Voltage

(V

CCP

)

Processor

Core Supply

Voltage

(V

CC

)

2.4 V to 3.3 V

Processor

Frequency

(MHz)

Package

FA80486SXSF-33

3.3 V

25

176-Lead

TQFP

2.7 V to 3.3 V

33

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INTEL82801 | 82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | Firmware Hub (FWH) |

| INTELDX2 | High-Performance 32-Bit Embedded Processor(高性能32位嵌入式處理器) |

| INTELDX4 | Embedded Write-Back Enhanced Processor(32位回復(fù)嵌入式增強(qiáng)型處理器) |

| IPS54511 | FULLY PROTECTED HIGH SIDE POWER MOSFET SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL740 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Graphics (GUI) Accelerator |

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

| INTELLI-INCH-LR-STARTER K | 制造商:ALL MOTION 功能描述:Intelli-Inch Stepper & Controller Starter Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。