- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373060 > K4D551638D-TC45 (SAMSUNG SEMICONDUCTOR CO. LTD.) CABLE ASSEMBLY; 2.9mm MALE TO 2.9mm MALE; 40 GHz CABLE PDF資料下載

參數(shù)資料

| 型號: | K4D551638D-TC45 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | CABLE ASSEMBLY; 2.9mm MALE TO 2.9mm MALE; 40 GHz CABLE |

| 中文描述: | 片256Mbit GDDR SDRAM內(nèi)存 |

| 文件頁數(shù): | 14/18頁 |

| 文件大?。?/td> | 230K |

| 代理商: | K4D551638D-TC45 |

256M GDDR SDRAM

K4D551638D-TC

- 14 -

Rev 1.8 (Oct. 2003)

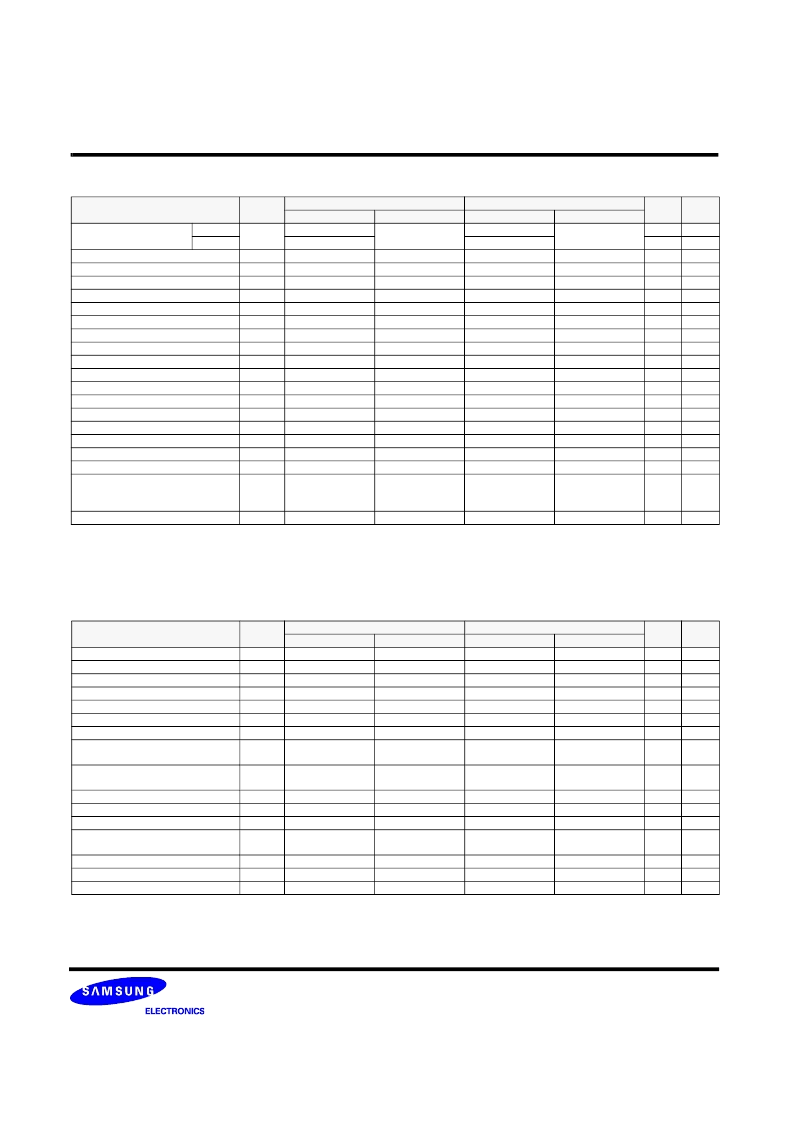

AC CHARACTERISTICS

Parameter

Symbol

-50

-60

Unit

Note

Min

5.0

-

0.45

0.45

-0.55

-0.65

-

0.9

0.4

0.72

0

0.25

0.4

0.35

0.35

0.6

0.6

0.4

0.4

tCLmin

or

tCHmin

tHP- 0.5

Max

Min

6.0

-

0.45

0.45

-0.6

-0.7

-

0.9

0.4

0.75

0

0.25

0.4

0.35

0.35

0.8

0.8

0.45

0.45

tCLmin

or

tCHmin

tHP-0.55

Max

CK cycle time

CL=3

CL=4

tCK

10

12

ns

ns

tCK

tCK

ns

ns

ns

tCK

tCK

tCK

ns

tCK

tCK

tCK

tCK

ns

ns

ns

ns

CK high level width

CK low level width

DQS out access time from CK

Output access time from CK

Data strobe edge to Dout edge

Read preamble

Read postamble

CK to valid DQS-in

DQS-In setup time

DQS-in hold time

DQS write postamble

DQS-In high level width

DQS-In low level width

Address and Control input setup

Address and Control input hold

DQ and DM setup time to DQS

DQ and DM hold time to DQS

tCH

tCL

tDQSCK

tAC

tDQSQ

tRPRE

tRPST

tDQSS

tWPRES

tWPREH

tWPST

tDQSH

tDQSL

tIS

tIH

tDS

tDH

0.55

0.55

0.55

0.65

0.4

1.1

0.6

1.28

-

-

0.6

-

-

-

-

-

-

0.55

0.55

0.6

0.7

0.45

1.1

0.6

1.25

-

-

0.6

-

-

-

-

-

-

1

Clock half period

tHP

-

-

ns

1

Data output hold time from DQS

tQH

-

-

ns

1

AC CHARACTERISTICS (I)

Note : 1. For normal write operation, even numbers of Din are to be written inside DRAM

Parameter

Symbol

-50

-60

Unit

Note

Min

12

14

8

4

2

4

2

Max

-

-

100K

-

-

-

-

Min

10

12

7

3

2

3

2

Max

-

-

100K

-

-

-

-

Row cycle time

Refresh row cycle time

Row active time

RAS to CAS delay for Read

RAS to CAS delay for Write

Row precharge time

Row active to Row active

Last data in to Row precharge @Nor-

mal Precharge

Last data in to Row precharge @Auto

Precharge

Last data in to Read command

Col. address to Col. address

Mode register set cycle time

Auto precharge write recovery + Pre-

charge

Exit self refresh to read command

Power down exit time

Refresh interval time

tRC

tRFC

tRAS

tRCDRD

tRCDWR

tRP

tRRD

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tWR

3

-

3

-

tCK

1

tWR_A

3

-

3

-

tCK

1

tCDLR

tCCD

tMRD

2

1

2

-

-

-

1

1

2

-

-

-

tCK

tCK

tCK

1

tDAL

7

-

6

-

tCK

tXSR

tPDEX

tREF

200

-

-

-

200

-

-

-

tCK

ns

us

1tCK+tIS

7.8

1tCK+tIS

7.8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4D551638D-TC50 | 256Mbit GDDR SDRAM |

| K4D551638D-TC60 | 256Mbit GDDR SDRAM |

| K4D623238B-GC | 64Mbit DDR SDRAM |

| K4D64163HF | 1M x 16Bit x 4 Banks Double Data Rate Synchronous DRAM |

| K4D64163HF-TC33 | 1M x 16Bit x 4 Banks Double Data Rate Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4D551638D-TC50 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D551638D-TC60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D551638F-LC40000 | 制造商:Samsung 功能描述:DDR SGRAM X16 TSOP2 - Trays 制造商:Samsung Semiconductor 功能描述:DRAM Chip GDDR SDRAM 256M-Bit 16Mx16 2.6V 66-Pin TSOP-II |

| K4D551638F-TC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

| K4D551638F-TC33 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit GDDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。