- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373062 > K4H560838F-UCC4 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Mb F-die DDR400 SDRAM Specification PDF資料下載

參數(shù)資料

| 型號(hào): | K4H560838F-UCC4 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Mb F-die DDR400 SDRAM Specification |

| 中文描述: | 256Mb的的F -模具支持DDR400內(nèi)存規(guī)格 |

| 文件頁(yè)數(shù): | 10/19頁(yè) |

| 文件大小: | 171K |

| 代理商: | K4H560838F-UCC4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

DDR SDRAM

DDR SDRAM 256Mb F-die (x8, x16)

Rev. 1.1 August. 2003

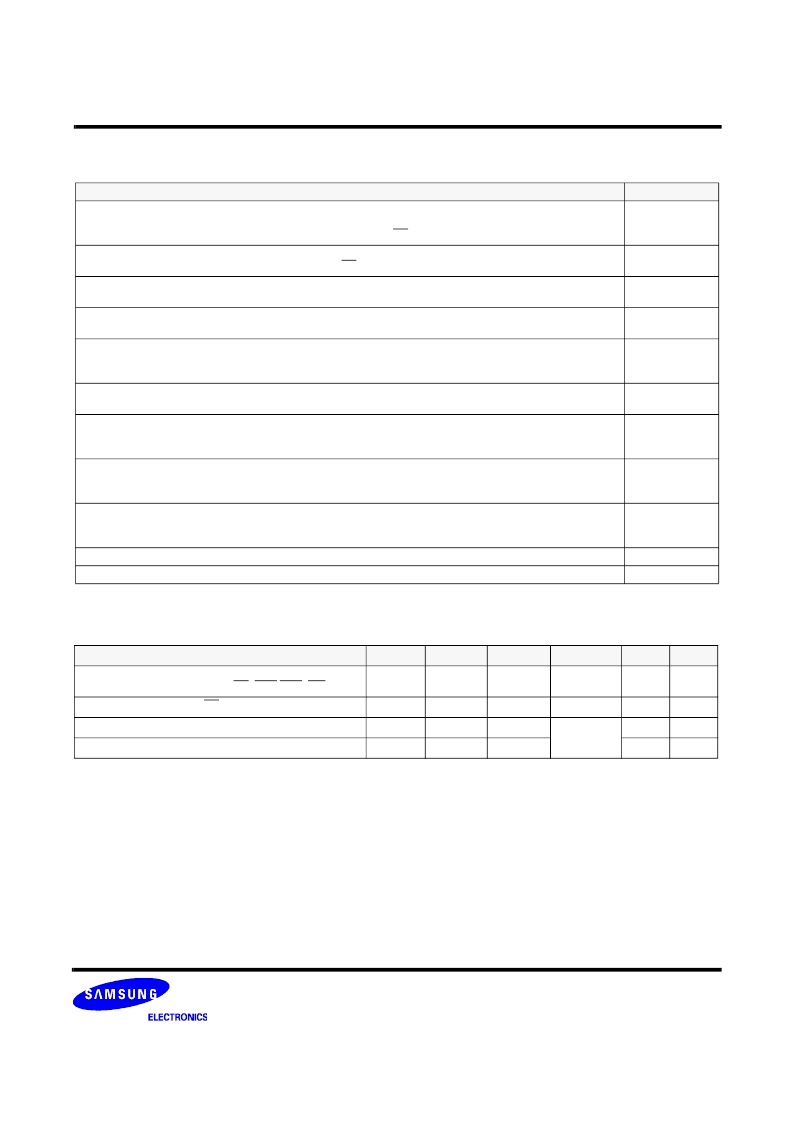

DDR SDRAM Spec Items & Test Conditions

Conditions

Symbol

Operating current - One bank Active-Precharge;

tRC=tRCmin; tCK=5ns for DDR400; DQ,DM and DQS inputs changing once per clock cycle;

address and control inputs changing once every two clock cycles; CS = high between valid commands.

Operating current - One bank operation ;

One bank open, BL=4, Reads

- Refer to the following page for detailed test condition; CS = high between valid commands.

Percharge power-down standby current;

All banks idle; power - down mode; CKE = <VIL(max); tCK=5ns for

DDR400; Vin = Vref for DQ,DQS and DM.

Precharge Floating standby current;

CS# > =VIH(min);All banks idle; CKE > = VIH(min); tCK=5ns for DDR400;

Address and other control inputs changing once per clock cycle; Vin = Vref for DQ,DQS and DM

Precharge Quiet standby current;

CS# > = VIH(min); All banks idle;

CKE > = VIH(min); tCK=5ns for DDR400; Address and other control inputs stable at >= VIH(min) or =<VIL(max);

Vin = Vref for DQ ,DQS and DM

Active power - down standby current ;

one bank active; power-down mode; CKE=< VIL (max); tCK=5ns

DDR400; Vin = Vref for DQ,DQS and DM

Active standby current;

CS# >= VIH(min); CKE>=VIH(min);

one bank active; active - precharge; tRC=tRASmax; tCK=5ns for DDR400; DQ, DQS and DM inputs changing twice

per clock cycle; address and other control inputs changing once per clock cycle

Operating current - burst read;

Burst length = 2; reads; continguous burst; One bank active; address and control

inputs changing once per clock cycle; CL=3 at 5ns for DDR400;

50% of data changing on every transfer; lout = 0 m

A

Operating current - burst write;

Burst length = 2; writes; continuous burst;

One bank active address and control inputs changing once per clock cycle; CL=3 at tCK=5ns for DDR400; DQ, DM

and DQS inputs changing twice per clock cycle, 50% of input data changing at every transfer

Auto refresh current;

tRC = tRFC(min) - 14*tCK for DDR400 at tCK=5ns;

Self refresh current;

CKE =< 0.2V; External clock on; tCK = 5ns for DDR400.

IDD0

IDD1

IDD2P

IDD2F

IDD2Q

IDD3P

IDD3N

IDD4R

IDD4W

IDD5

IDD6

Input/Output Capacitance

(V

DD

=2.6, V

DDQ

=2.6V, T

A

= 25

°

C, f=1MHz)

Parameter

Symbol

Min

Max

Delta

Unit

Note

Input capacitance

(A0 ~ A12, BA0 ~ BA1, CKE, CS, RAS,CAS, WE)

CIN1

2

3

0.5

pF

4

Input capacitance( CK, CK )

CIN2

2

3

0.25

pF

4

Data & DQS input/output capacitance

COUT

4

5

0.5

pF

1,2,3,4

Input capacitance(DM for 8, UDM/LDM for x16)

CIN3

4

5

pF

1,2,3,4

1.These values are guaranteed by design and are tested on a sample basis only.

2. Although DM is an input -only pin, the input capacitance of this pin must model the input capacitance of the DQ and DQS pins.

This is required to match signal propagation times of DQ, DQS, and DM in the system.

3. Unused pins are tied to ground.

4. This parameteer is sampled. VDDQ = +2.6V +0.1V, VDD = +2.6V +0.1V, f=100MHz, tA=25

°

C, Vout(dc) =

VDDQ/2, Vout(peak to peak) = 0.2V. DM inputs are grouped with I/O pins - reflecting the fact that they are matched in loading

(to facilitate trace matching at the board level).

Note :

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4H560838F-UCCC | 256Mb F-die DDR400 SDRAM Specification |

| K4H560838D-TCA0 | 128Mb DDR SDRAM |

| K4H560838D-TCA2 | 128Mb DDR SDRAM |

| K4H560838D-TCB0 | 10-Bit, 32 kSPS ADC Serial Out, uProcessor Periph./Standalone, 11 Ch. 20-SOIC |

| K4H560838D-TCC4 | 256Mb D-die DDR400 SDRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4H560838F-UCCC | 制造商:Samsung Electro-Mechanics 功能描述:32M X 8 DDR DRAM, 0.65 ns, 66 Pin Plastic SMT |

| K4H560838H | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Product Guide |

| K4H560838H-UC/LA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb H-die DDR SDRAM Specification |

| K4H560838H-UC/LB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb H-die DDR SDRAM Specification |

| K4H560838H-UC/LB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mb H-die DDR SDRAM Specification |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。