- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373080 > K7B323625M-QC65 (SAMSUNG SEMICONDUCTOR CO. LTD.) 1Mx36 & 2Mx18 Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | K7B323625M-QC65 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 元件分類: | DRAM |

| 英文描述: | 1Mx36 & 2Mx18 Synchronous SRAM |

| 中文描述: | 1Mx36 |

| 文件頁數(shù): | 10/19頁 |

| 文件大?。?/td> | 264K |

| 代理商: | K7B323625M-QC65 |

K7B321825M

1Mx36 & 2Mx18 Synchronous SRAM

- 10 -

Rev 2.0

Nov. 2003

K7B323625M

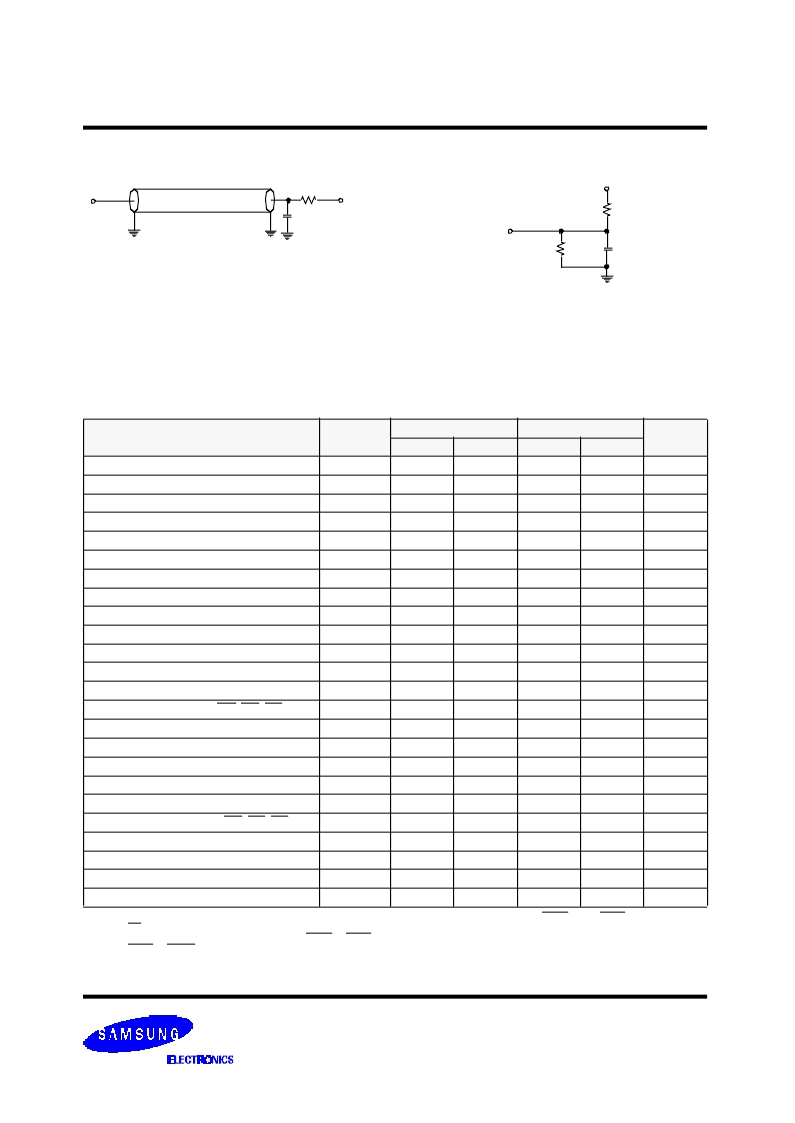

Output Load(B),

(for t

LZC

, t

LZOE

, t

HZOE

& t

HZC

)

Dout

353

/

1538

5pF*

+3.3V for 3.3V I/O

/+2.5V for 2.5V I/O

319

/

1667

Fig. 1

* Including Scope and Jig Capacitance

Output Load(A)

Dout

Zo=50

RL=50

VL=1.5V for 3.3V I/O

V

DDQ

/2 for 2.5V I/O

30pF*

AC TIMING CHARACTERISTICS

(V

DD

=3.3V+0.165V/-0.165V, T

A

=0

°

C to +70

°

C)

Notes

:

1. All address inputs must meet the specified setup and hold times for all rising clock edges whenever ADSC and/or ADSP is sampled low and

CS is sampled low. All other synchronous inputs must meet the specified setup and hold times whenever this device is chip selected.

2. Both chip selects must be active whenever ADSC or ADSP is sampled low in order for the this device to remain enabled.

3. ADSC or ADSP must not be asserted for at least 2 Clock after leaving ZZ state.

PARAMETER

SYMBOL

-65

-75

UNIT

MIN

MAX

MIN

MAX

Cycle Time

t

CYC

7.5

-

8.5

-

ns

Clock Access Time

t

CD

-

6.5

-

7.5

ns

Output Enable to Data Valid

t

OE

-

3.5

-

3.5

ns

Clock High to Output Low-Z

t

LZC

2.5

-

2.5

-

ns

Output Hold from Clock High

t

OH

2.5

-

2.5

-

ns

Output Enable Low to Output Low-Z

t

LZOE

0

-

0

-

ns

Output Enable High to Output High-Z

t

HZOE

-

3.5

-

3.5

ns

Clock High to Output High-Z

t

HZC

-

3.8

-

4.0

ns

Clock High Pulse Width

t

CH

2.2

-

2.5

-

ns

Clock Low Pulse Width

t

CL

2.2

-

2.5

-

ns

Address Setup to Clock High

t

AS

1.5

-

2.0

-

ns

Address Status Setup to Clock High

t

SS

1.5

-

2.0

-

ns

Data Setup to Clock High

t

DS

1.5

-

2.0

-

ns

Write Setup to Clock High (GW, BW, WE

X

)

t

WS

1.5

-

2.0

-

ns

Address Advance Setup to Clock High

t

ADVS

1.5

-

2.0

-

ns

Chip Select Setup to Clock High

t

CSS

1.5

-

2.0

-

ns

Address Hold from Clock High

t

AH

0.5

-

0.5

-

ns

Address Status Hold from Clock High

t

SH

0.5

-

0.5

-

ns

Data Hold from Clock High

t

DH

0.5

-

0.5

-

ns

Write Hold from Clock High (GW, BW, WE

X

)

t

WH

0.5

-

0.5

-

ns

Address Advance Hold from Clock High

t

ADVH

0.5

-

0.5

-

ns

Chip Select Hold from Clock High

t

CSH

0.5

-

0.5

-

ns

ZZ High to Power Down

t

PDS

2

-

2

-

cycle

ZZ Low to Power Up

t

PUS

2

-

2

-

cycle

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7B323625M-QC6575 | 1Mx36 & 2Mx18 Synchronous SRAM |

| K7B323625M | 1Mx36 & 2Mx18 Synchronous SRAM |

| K7B323625M-QC75 | 1Mx36 & 2Mx18 Synchronous SRAM |

| K7A321800M | 1Mx36 & 2Mx18 Synchronous SRAM |

| K7A321800M-QC14 | 1Mx36 & 2Mx18 Synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7B323625M-QC6575 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 Synchronous SRAM |

| K7B323625M-QC75 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 Synchronous SRAM |

| K7B323635C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Mx36 & 2Mx18 Synchronous SRAM |

| K7B323635C-PI75000 | 制造商:Samsung SDI 功能描述: |

| K7B401825B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Kx36 & 256Kx18 Synchronous SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。