- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224103 > K7R161884B (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Kx36 & 1Mx18 QDR II b4 SRAM PDF資料下載

參數(shù)資料

| 型號: | K7R161884B |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Kx36 & 1Mx18 QDR II b4 SRAM |

| 中文描述: | 512Kx36 |

| 文件頁數(shù): | 3/18頁 |

| 文件大小: | 418K |

| 代理商: | K7R161884B |

- 11 -

Rev 3.1

July. 2004

512Kx36 & 1Mx18 QDRTM II b4 SRAM

K7R163684B

K7R161884B

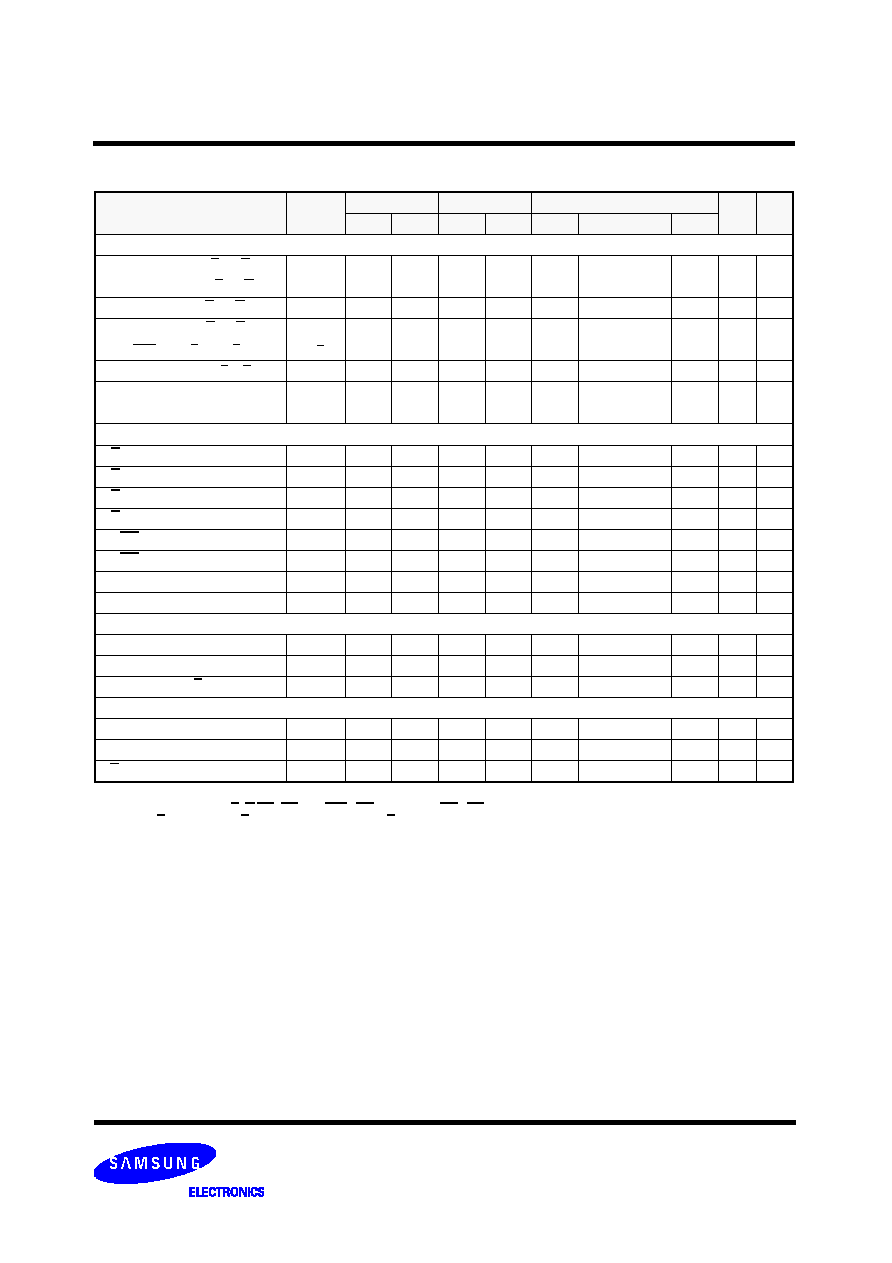

AC TIMING CHARACTERISTICS(VDD=1.8V±0.1V, TA=0°C to +70°C)

Notes: 1. All address inputs must meet the specified setup and hold times for all latching clock edges.

2. Control singles are R, W,BW0,BW1 and (NW0, NW1, for x8) and (BW2, BW3, also for x36)

3. If C,C are tied high, K,K become the references for C,C timing parameters.

4. To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ.

The specs as shown do not imply bus contention beacuse tCHQX1 is a MIN parameter that is worst case at totally different test conditions

(0

°C, 1.9V) than tCHQZ, which is a MAX parameter(worst case at 70°C, 1.7V)

It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

5. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

6. Vdd slew rate must be less than 0.1V DC per 50 ns for DLL lock retention. DLL lock time begins once Vdd and input clock are stable.

7. Echo clock is very tightly controlled to data valid/data hold. By design, there is a

± 0.1 ns variation from echo clock to data.

The data sheet parameters reflect tester guardbands and test setup variations.

PARAMETER

SYMBOL

-30

-25

-20

-16

UNIT NOTE

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

Clock

Clock Cycle Time (K, K, C, C)tKHKH

3.30

5.25

4.00

6.30

5.00

7.88

6.00

8.40

ns

Clock Phase Jitter (K, K, C, C)tKC var

0.20

ns

5

Clock High Time (K, K, C, C)tKHKL

1.32

1.60

2.00

2.40

ns

Clock Low Time (K, K, C, C)tKLKH

1.32

1.60

2.00

2.40

ns

Clock to Clock (K

↑ → K↑, C↑ → C↑)

tKHKH

1.49

1.80

2.20

2.70

ns

Clock to data clock (K

↑ → C↑, K↑→ C↑)

tKHCH

0.00

1.45

0.00

1.80

0.00

2.30

0.00

2.80

ns

DLL Lock Time (K, C)

tKC lock

1024

cycle

6

K Static to DLL reset

tKC reset

30

ns

Output Times

C, C High to Output Valid

tCHQV

0.45

0.50

ns

3

C, C High to Output Hold

tCHQX

-0.45

-0.50

ns

3

C, C High to Echo Clock Valid

tCHCQV

0.45

0.50

ns

C, C High to Echo Clock Hold

tCHCQX

-0.45

-0.50

ns

CQ, CQ High to Output Valid

tCQHQV

0.27

0.30

0.35

0.40

ns

7

CQ, CQ High to Output Hold

tCQHQX

-0.27

-0.30

-0.35

-0.40

ns

7

C, High to Output High-Z

tCHQZ

0.45

0.50

ns

3

C, High to Output Low-Z

tCHQX1

-0.45

-0.50

ns

3

Setup Times

Address valid to K rising edge

tAVKH

0.40

0.50

0.60

0.70

ns

Control inputs valid to K rising edge

tIVKH

0.40

0.50

0.60

0.70

ns

2

Data-in valid to K, K rising edge

tDVKH

0.30

0.35

0.40

0.50

ns

Hold Times

K rising edge to address hold

tKHAX

0.40

0.50

0.60

0.70

ns

K rising edge to control inputs hold

tKHIX

0.40

0.50

0.60

0.70

ns

K, K rising edge to data-in hold

tKHDX

0.30

0.35

0.40

0.50

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7R163684B | 512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R323682 | 1Mx36 & 2Mx18 & 4Mx9 QDRTM II b2 SRAM |

| K971 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

| K972 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

| K973 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7R161884B-FC16 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R161884B-FC20 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R161884B-FC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R161884B-FC30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R163682B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 & 2Mx9 QDRTM II b2 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。