- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373162 > KM68V1002CI (SAMSUNG SEMICONDUCTOR CO. LTD.) 128K x 8 Bit High-Speed CMOS Static RAM(3.3V Operating)(128K x 8位高速CMOS 靜態(tài) RAM) PDF資料下載

參數(shù)資料

| 型號: | KM68V1002CI |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128K x 8 Bit High-Speed CMOS Static RAM(3.3V Operating)(128K x 8位高速CMOS 靜態(tài) RAM) |

| 中文描述: | 128K的× 8位高速CMOS靜態(tài)RAM(3.3V的工作)(128K的× 8位高速的CMOS靜態(tài)RAM)的 |

| 文件頁數(shù): | 7/9頁 |

| 文件大小: | 131K |

| 代理商: | KM68V1002CI |

KM68V1002C/CL, KM68V1002CI/CLI

CMOS SRAM

PRELIMINARY

Revision 0.0

August 1998

- 7 -

NOTES

(WRITE CYCLE)

1. All write cycle timing is referenced from the last valid address to the first transition address.

2. A write occurs during the overlap of a low CS and WE. A write begins at the latest transition CS going low and WE going low ;

A write ends at the earliest transition CS going high or WE going high. t

WP

is measured from the beginning of write to the end of

write.

3. t

CW

is measured from the later of CS going low to end of write.

4. t

AS

is measured from the address valid to the beginning of write.

5. t

WR

is measured from the end of write to the address change. t

WR

applied in case a write ends as CS or WE going high.

6. If OE, CS and WE are in the Read Mode during this period, the I/O pins are in the output low-Z state. Inputs of opposite phase

of the output must not be applied because bus contention can occur.

7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

8. If CS goes low simultaneously with WE going or after WE going low, the outputs remain high impedance state.

9. Dout is the read data of the new address.

10. When CS is low : I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be

applied.

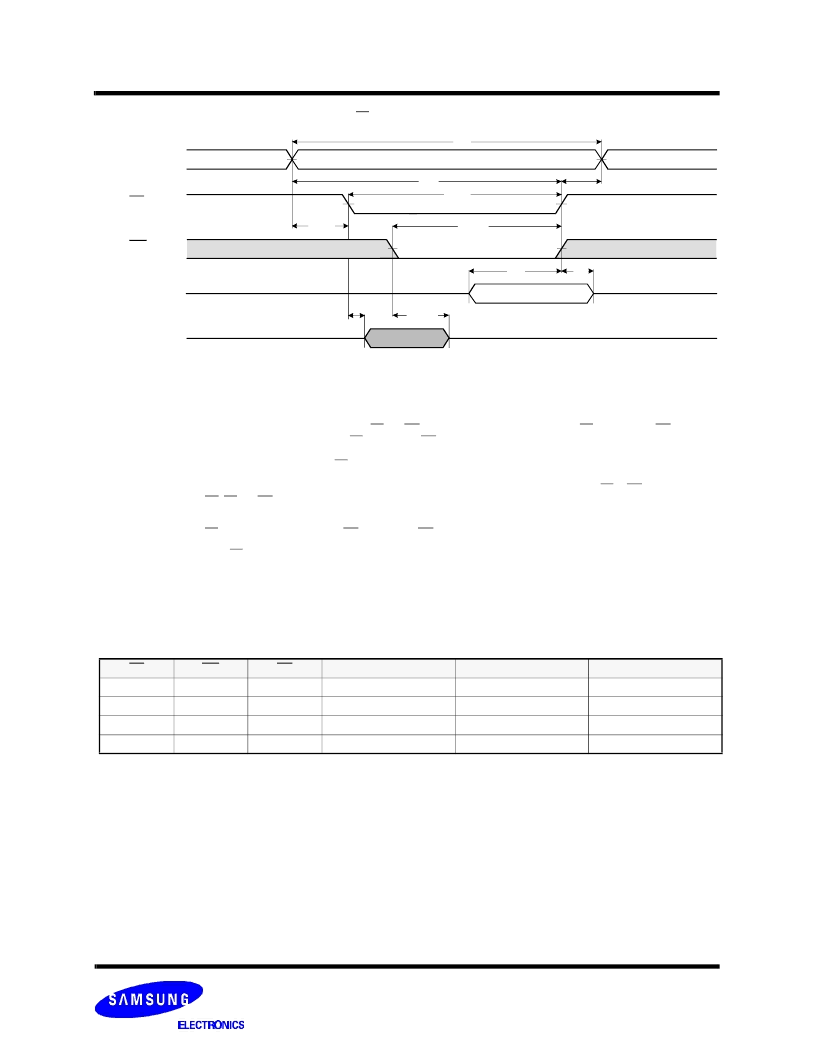

TIMING WAVEFORM OF WRITE CYCLE(3)

(CS

=

Controlled)

Address

CS

t

AW

t

DW

t

DH

Data Valid

WE

Data in

Data out

High-Z

High-Z(8)

t

CW(3)

t

WP(2)

t

AS(4)

t

WC

t

WR(5)

High-Z

High-Z

t

LZ

t

WHZ(6)

FUNCTIONAL DESCRIPTION

* NOTE : X means Don

′

t Care.

CS

WE

OE

Mode

I/O Pin

Supply Current

H

X

X*

Not Select

High-Z

I

SB

, I

SB1

L

H

H

Output Disable

High-Z

I

CC

L

H

L

Read

D

OUT

I

CC

L

L

X

Write

D

IN

I

CC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM68V257C | 32K x 8 Bit High-Speed CMOS Static RAM (3.3V Operating)(32K x 8位高速CMOS 靜態(tài) RAM) |

| KM68V257E | 32K x 8 Bit High-Speed CMOS Static RAM (3.3V Operating)(32K x 8位高速CMOS 靜態(tài) RAM) |

| KM68V257EI | 32K x 8 Bit High-Speed CMOS Static RAM (3.3V Operating)(32K x 8位高速CMOS 靜態(tài) RAM) |

| KM68V4002B | 512Kx8 Bit High Speed Static RAM(3.3V Operating)(512K x8位高速CMOS 靜態(tài) RAM) |

| KM68V4002BI | 512Kx8 Bit High Speed Static RAM(3.3V Operating)(512K x8位高速CMOS 靜態(tài) RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM68V2000ALTGI-7L | 制造商:Samsung Electro-Mechanics 功能描述:256K X 8 STANDARD SRAM, 70 ns, PDSO32 |

| KM68V257C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257C-15 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257C-17 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High Speed Static RAM(3.3V Operating), Evolutionary Pin out. |

| KM68V257E | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32Kx8 Bit High-Speed CMOS Static RAM (3.3V Operating) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。