- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373162 > KM736FV4011 (SAMSUNG SEMICONDUCTOR CO. LTD.) 128Kx36 Synchronous SRAM(128Kx36位同步靜態(tài) RAM) PDF資料下載

參數(shù)資料

| 型號: | KM736FV4011 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128Kx36 Synchronous SRAM(128Kx36位同步靜態(tài) RAM) |

| 中文描述: | 128K × 36至同步SRAM(128K × 36至位同步靜態(tài)內(nèi)存) |

| 文件頁數(shù): | 9/13頁 |

| 文件大小: | 297K |

| 代理商: | KM736FV4011 |

PRELIMINARY

Rev 0.2

Dec. 1997

KM718FV4011

128Kx36 & 256Kx18 SRAM

- 9 -

KM736FV4011

DC Electrical Characteristics

NOTE

: 1. Measured at V

OUT

=V

DDQ

/2. I

OUT

=(V

DDQ

/2)/(RQ/5)

±

10% @V

OUT

=V

DDQ

/2.

Parameter

Symbol

Min

Typ

Max

Unit

Note

Impedance Control Resistor Range

RQ

175

250

350

-

Driver Impedance

Z

D

RQ/5-10%

-

RQ/5+10%

1

PROGRAMMABLE IMPEDANCE OUTPUT BUFFER OPERATION

The designer can program the SRAM

′

s output buffer impedance by terminating the ZQ pin to V

SS

through a precision resistor(RQ).

The value of RQ is five times the output impedance desired. For example, 250

resistor will give an output impedance of 50

. The

allowable range of RQ to guarantee impedance matching with a tolerance of 10% is between 175

and 350

. Impedance updates

occur early in cycles that do not activate the outputs, such as deselect cycles. They may also occur in cycles initiated with G high. In

all cases impedance updates are transparent to the user and do not produce access time "push-outs" or other anomalous behavior in

the SRAM. Periodic readjustment is necessary as the impedance is greatly affected by drifts in supply voltage and temperature.

Impedance updates occur no more often than every 32clock cycles. Clock cycles are counted whether the SRAM is selected or not

and proceed regardless of the type of cycle being executed. Therefore, the user can be assured that after 33continuous read cycles

have occurred, an impedance update will occur the next time SS or G are high at a rising edge of the K clock. There are no power up

requirements for the SRAM. However, to guarantee optimum output driver impedance after power up, the SRAM needs 1024 non-

read cycles.

AC Electrical Characteristics

Parameter

Symbol

Min

Typ

Max

Unit

Note

Output Impedance Update G Setup Time

t

GHKH

0.5

-

-

ns

-

Output Impedance Update G Hold Time

t

KHGX

1.0

-

-

ns

-

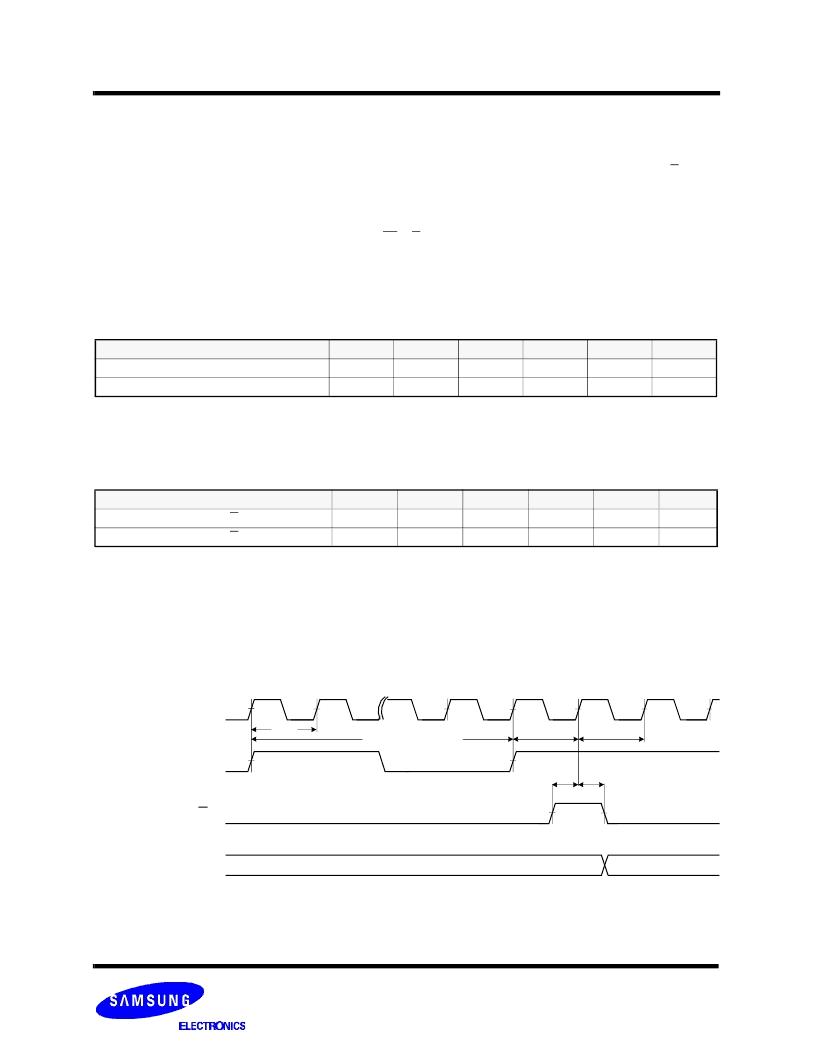

TIMING WAVEFORMS OF Driver Impedance Update Control

1

32

33

34

35

K Clock

SRAM Internal Clock

(devided by 32)

Output Enable, G

SRAM Driver

Impedance

Code

Transfer

Old Code

New Code

Code

Update

Code Generation Time

t

KHKH

t

KHGX

t

GHKH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM718FV4021 | 256Kx18 Synchronous SRAM(256Kx18位同步靜態(tài) RAM) |

| KM736FV4021 | 128Kx36 Synchronous SRAM(128Kx36位同步靜態(tài) RAM) |

| KM718FV4022 | 256Kx18 Synchronous SRAM(256Kx18位同步靜態(tài) RAM) |

| KM736FV4022 | 128Kx36 Synchronous SRAM(128Kx36位同步靜態(tài) RAM) |

| KM718V089 | 512Kx36 & 1Mx18 Synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM736FV4021 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Kx36 & 256Kx18 Synchronous Pipelined SRAM |

| KM736FV4021H-5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Kx36 & 256Kx18 Synchronous Pipelined SRAM |

| KM736FV4021H-6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Kx36 & 256Kx18 Synchronous Pipelined SRAM |

| KM736FV4021H-7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Kx36 & 256Kx18 Synchronous Pipelined SRAM |

| KM736N | 制造商:FRONTIER 制造商全稱:Frontier Electronics. 功能描述:10mm Adjustable Shielded RF Coil (I) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。