- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄11591 > KSZ8842-16MBLI (Micrel Inc)IC ETHERNET SW 2PORT 100-LFBGA PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8842-16MBLI |

| 廠商: | Micrel Inc |

| 文件頁(yè)數(shù): | 79/141頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ETHERNET SW 2PORT 100-LFBGA |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 控制器類(lèi)型: | 以太網(wǎng)開(kāi)關(guān)控制器 |

| 接口: | PCI |

| 電源電壓: | 3.1 V ~ 3.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 100-LBGA |

| 供應(yīng)商設(shè)備封裝: | 100-LFBGA |

| 包裝: | 托盤(pán) |

| 產(chǎn)品目錄頁(yè)面: | 1081 (CN2011-ZH PDF) |

| 其它名稱(chēng): | 576-3504 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)當(dāng)前第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)

Micrel, Inc.

KSZ8842-16/32 MQL/MVL/MVLI/MBL

October 2007

42

M9999-102207-1.9

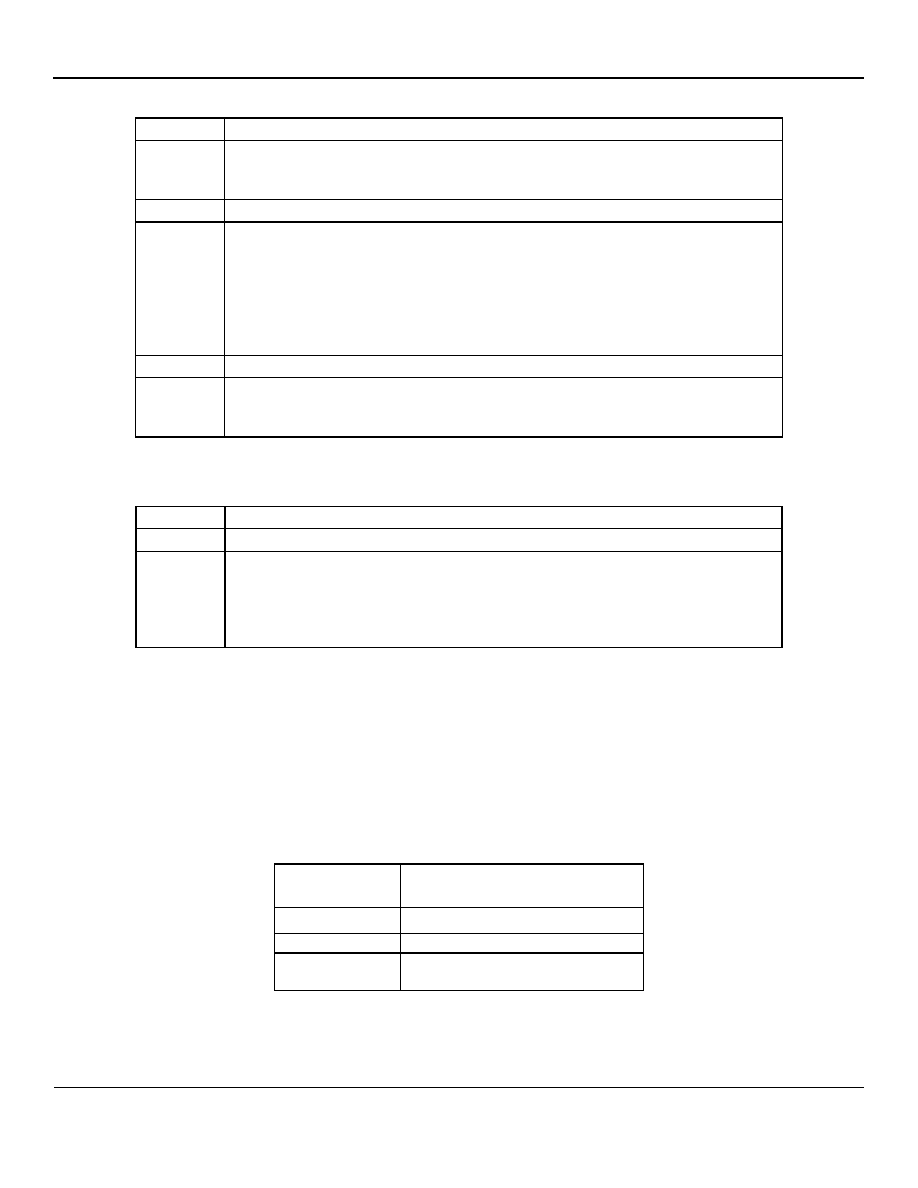

Bit

Description

15

TXIC Transmit Interrupt on Completion

When bit is set, the KSZ8842M sets the transmit interrupt after the present frame has been

transmitted.

14-10

Reserved

9-8

TXDPN Transmit Destination Port Number

When bit is set, this field indicates the destination port(s) where the packet is forwarded

from host system. Set bit 8 to indicate that port 1 is the destination port. Set bit 9 to

indicate that port 2 is the destination port.

Setting all ports to 1 causes the switch engine to broadcast the packet to both ports.

Setting all bits to 0 has no effect. The internal switch engine forwards the packets

according to the switching algorithm in its MAC lookup table.

7-6

Reserved

5-0

TXFID Transmit Frame ID

This field specifies the frame ID that is used to identify the frame and its associated status

information in the transmit status register TXSR[5:0].

Table 4. Transmit Control Word Bit Fields

The transmit Byte Count specifies the total number of bytes to be transmitted from the TXQ. Its format is given in Table 5.

Bit

Description

15-11

Reserved

10-0

TXBC Transmit Byte Count

Transmit Byte Count. Hardware uses the byte count information to conserve the TX buffer

memory for better utilization of the packet memory.

Note: The hardware behavior is unknown if an incorrect byte count information is written to

this field. Writing a 0 value to this field is not permitted.

Table 5. Transmit Byte Count Format

The data area contains six bytes of Destination Address (DA) followed by six bytes of Source Address (SA), followed by a

variable-length number of bytes. On transmit, all bytes are provided by the CPU, including the source address. The

KSZ8842M does not insert its own source address. The 802.3 Frame Length word (Frame Type in Ethernet) is not

interpreted by the KSZ8842M. It is treated transparently as data for transmit operations.

Receive Queue (RXQ) Frame Format

The frame format for the receive queue is shown in Table 6. The first word contains the status information for the frame

received. The second word is the total number of bytes of the RX frame. Following that is the packet data area. The

packet data area holds the frame itself. It may or may not include the CRC checksum depending upon whether hardware

CRC stripping is enabled.

Packet Memory

Address Offset

Bit 15

Bit 0

2

nd Byte

1

st Byte

0

Status Word

2

Byte Count

4 - up

Packet Data

(maximum size is 1916)

Table 6. Receive Queue Frame Format

For receive, the packet receive status always reflects the receive status of the packet received in the current RX packet

memory (see Table 7). The RXSR register indicates the status of the current received frame.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC4259ACGW#PBF | IC CTRLR POE QUAD AC DISC 36SSOP |

| VNC2-64Q1B-REEL | IC USB HOST/DEVICE CTRL 64-QFN |

| V72A48C400BF2 | CONVERTER MOD DC/DC 48V 400W |

| PIC16F1827-E/SO | MCU PIC 8BIT 4K FLASH 18-SOIC |

| PIC16F1826T-I/MV | MCU PIC 8BIT 2K FLASH 28-UQFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8842-16MBLI TR | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch + Generic (8, 16-Bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MQL | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MQL-EVAL | 功能描述:以太網(wǎng)開(kāi)發(fā)工具 KSZ8842-16MQL Evaluation Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類(lèi)型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類(lèi)型:RMII 工作電源電壓: |

| KSZ8842-16MVL | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-16MVL TR | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + Generic (8, 16-bit) bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。