- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30731 > LC72711LW (SANYO SEMICONDUCTOR CO LTD) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | LC72711LW |

| 廠商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, SQFP-64 |

| 文件頁數(shù): | 11/26頁 |

| 文件大?。?/td> | 157K |

| 代理商: | LC72711LW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

LC72711W, 72711LW

No.6167-19/26

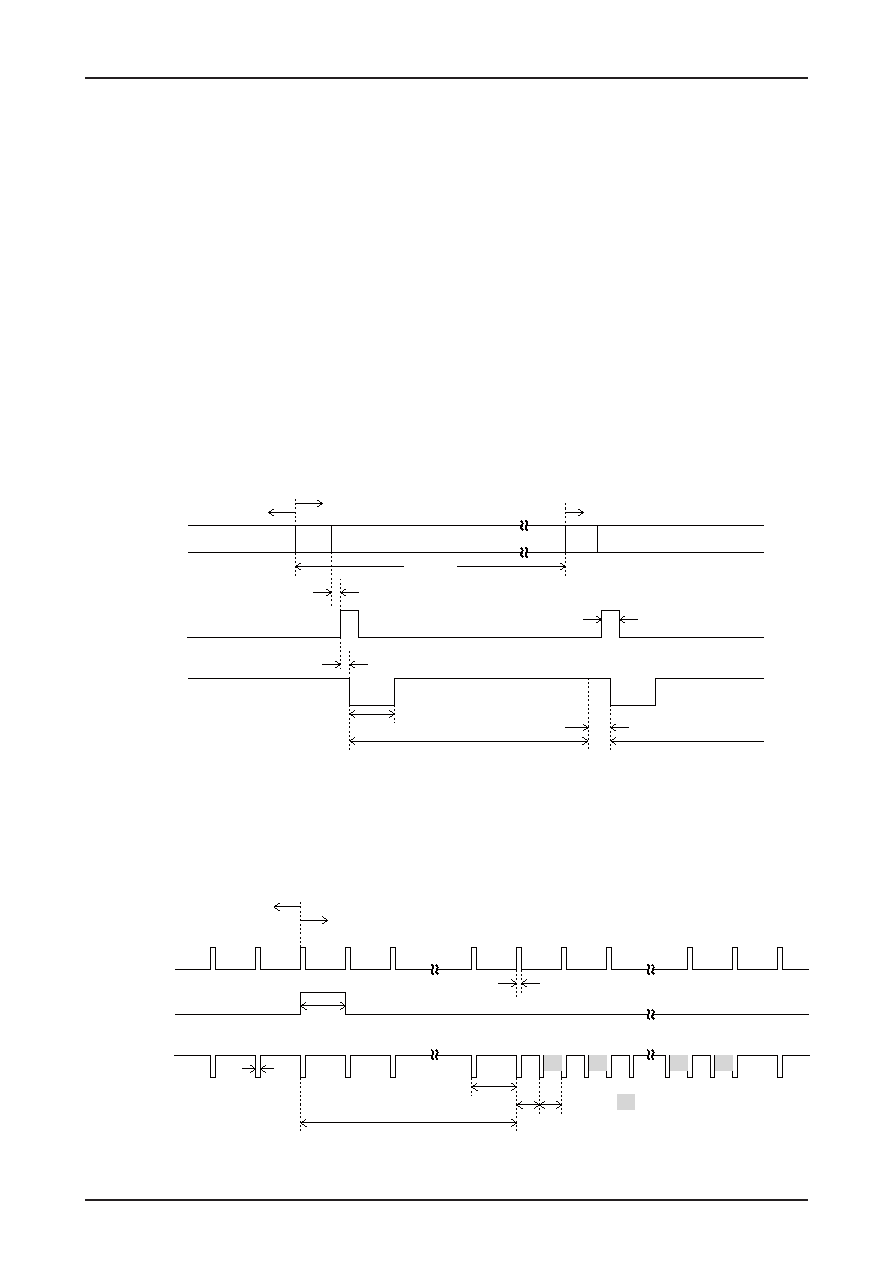

Notes on Data Output Timing (Relationship with the received data)

Figure 3 shows the timing relationship between the received data and the interrupt control signal (INT). However, the

delay from the actual received signal due to demodulation operations in MSK demodulation blocks is ignored.

Block synchronization is established by discriminating the BIC code. As shown in figure 3, the data for the nth packet

can be output during reception of the following packet (number n+1).

Figure 4 shows the output timing for post-vertical correction data. In vertical correction, the data for a single frame is

stored in memory and the correction operation is performed if frame synchronization was established and it was not

possible to correct all the packet data in horizontal correction. The timing with which vertical correction is started is the

start of the frame. Horizontal correction is performed for each packet while packets 1 through 28 in the nth frame are

being received, and this data is passed to the CPU interface. Vertical correction is performed for the data from the

previous frame (frame n-1) in the unused time periods during that processing.

The vertical correction data consists of 190 blocks that are output, and this data is output at the rate of one block for

every block received, in order starting at the time the 29th packet (block) is received. Only data from the data blocks in

the FM multiplex broadcast frame structure is output, and the last block (block 190) is output during reception of the

218th block.

As indicated previously (page 17) packet data that was, for example, corrected completely by horizontal correction, is

not output in the vertical correction output data. (The INT signal is not issued.) However, the order in which the

horizontal output is produced is not speeded up by the amount of the packet data that is not output. For example, if data

packets 1 to 100 were corrected by horizontal correction, output of the post-vertical correction packet data for packet

101 will not occur at the reception position of block number 29 in figure 4, but at the reception position for packet data

number 129.

BIC

18ms

300ns max

62.5s

68s

Packet n-1

Packet n+1

Packet n data

1ms

Recieved

data

BCK

INT

Data cannot

be guaranteed

Packet n data output

Output period for

packet n+1 data

BCK

FCK

INT

1ms

Output periods for

post-vertical correction

data from the previous

frame.

9ms

62.5s

18ms

271

Recieved block

signal

272

1

2

3

2

1

28

29

30

31

220

219

218

189

190

First

frame

nth frame

18ms28=504ms

Figure 3 Received Data, Block Synchronization, and Data Output Timing

Figure 4 Post-Vertical Correction Data Output Timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72713W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72713W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72714W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72714W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72715PW | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72711LW-E | 制造商:ON Semiconductor 功能描述:DARC DECODE-LSI - Trays |

| LC72711LWHS-E | 功能描述:射頻接收器 RoHS:否 制造商:Skyworks Solutions, Inc. 類型:GPS Receiver 封裝 / 箱體:QFN-24 工作頻率:4.092 MHz 工作電源電壓:3.3 V 封裝:Reel |

| LC72711W | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast DARC Receiver IC |

| LC72711W_12 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast (DARC) Receiver IC |

| LC72713W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。