- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30731 > LC72714W SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | LC72714W |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, SQFP-64 |

| 文件頁數(shù): | 14/29頁 |

| 文件大小: | 158K |

| 代理商: | LC72714W |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

LC72714W

No.6871-21/29

Control Program Compatibility

This IC allows the majority of the control software used to be compatible with Sanyo’s other FM multiplex ICs, in

particular, the LC72700E, LC72705E, LC72706E, LC72708E, and LC72709E(W). However, the following aspects of

the control software require modification.

Values of the register addresses

The addresses of the allowable BIC error count, synchronization error protection count, control registers, the layer 4

CRC register, and other registers have been modified.

The CCB address for serial I/O over a CCB bus has not been changed.

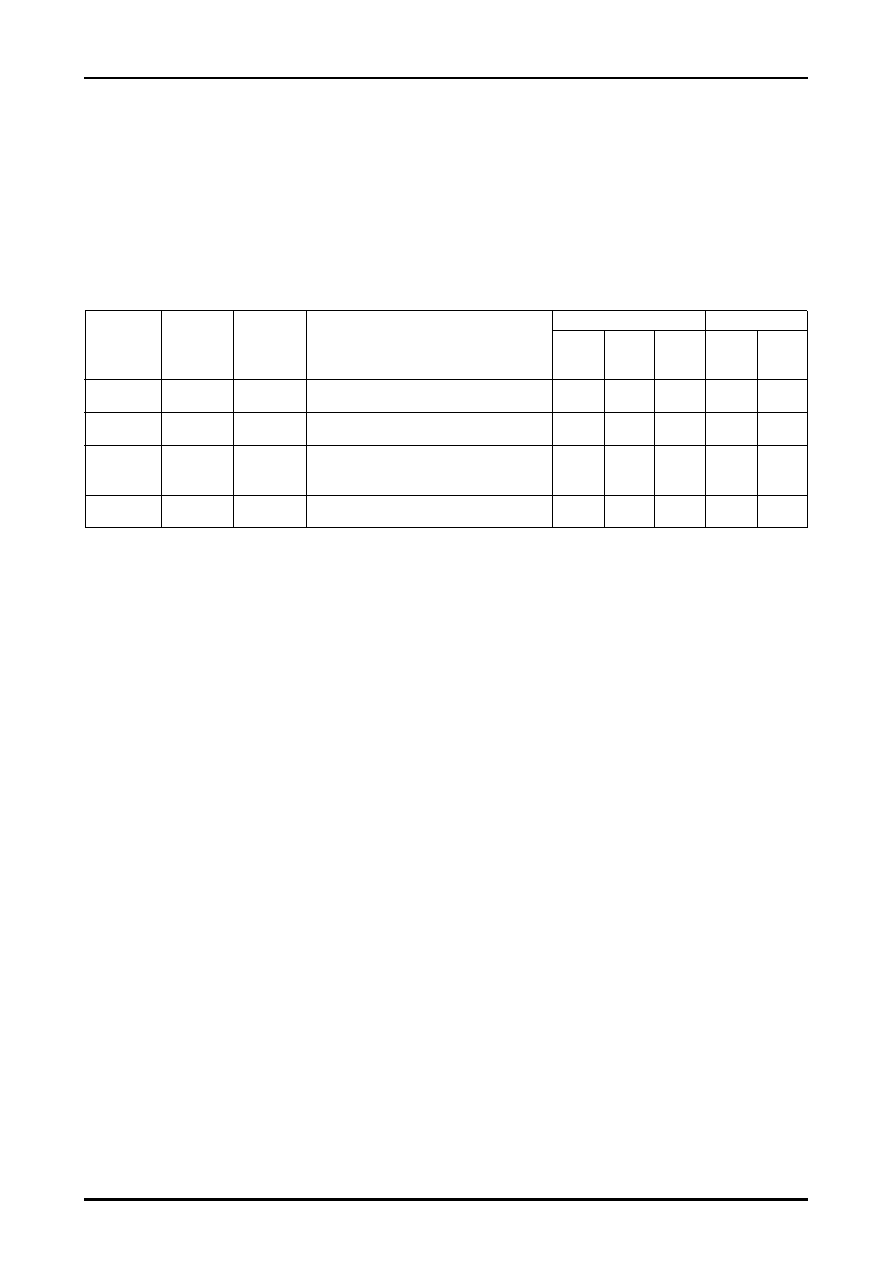

INT signal output timing

The INT signal output timing for data output is as follows. A circle ("O") indicates that INT is output, and a cross

("X") indicates that the signal is not output.

Control

Horizontal correction output

Vertical correction output

Item

register 1

register 2

Operational overview

Correct

Incorrect

Correct

bit 5,

bit 2,

data

Parity

data

NG

INT_MOVE

VEC_OUT

Default value

L

H

Operation identical to that of the LC72705/06E

Ο

Ο *1

and LC72708/09E(W)

Combination 1

H

Operation identical to that of the LC72700E

ΟΟ

Ο

Ο *2

Ο

All data is output

The output data selection conditions are cleared,

Combination 2

H

L

but there is no vertical correction output when

ΟΟ

Ο

Ο *3

Ο

vertical correction is not performed

Combination 3

L

H

The output data selection conditions are retained,

Ο

ΟΟ

but all of the vertical correction output is output

Notes: 1. Data for which horizontal correction failed, but for which vertical correction succeeded is output.

2. All data is output.

3. If there is data for which horizontal correction failed, the post-vertical correction data for that data is output, regardless of whether or not vertical

correction succeeded.

(If the IC performs vertical correction, post-vertical correction data will be output.)

Notes on Output Data Selection after Tuning (Reference)

When building an FM multiplex reception system, a tuning system is an absolute necessity. However, if it is

unacceptable for the IC to output data from the old station after tuning to a new station, the application must perform

the following processing.

(1) At the same time as tuning a new station, the application must set bit 4 (SYNC_RST) in control register 1 to set the

synchronization circuit to the unsynchronized state.

(2) Under the default settings, after the synchronization reset applications must acquire data according to the issued INT

signal.

The post-vertical correction output is not provided by the IC until frame synchronization has been established for the

new station after tuning and the first vertical correction operation has been performed.

(3) If bit 2 (VEC_OUT) in control register 2 has been enabled, applications must not use the post-vertical correction

output (data for which bit 7 in the status register is high) until frame synchronization has been reestablished.

This IC performs the portion of the DARC FM multiplex processing through layer 2 error correction without requiring

any special control operations. The IC itself cannot determine if the contents of the received data have changed or if a

new station has been tuned. This means that applications must use the procedure described above for this IC not to

output old data and only output the new data. Another point is that in IC synchronization, although it is rare for the old

station and the new station to be frame synchronized, applications need to perform the processing in item 1 above to

cancel frame synchronization forward protection period.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72715PW | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72720NM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72720NM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72720N | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| LC72720N | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72715PW | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Mobile FM Multiplex Broadcast IC with On-Chip VICS Decoder |

| LC72717PW | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast (DARC) Receiver IC |

| LC72720 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72720M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72720N | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。