- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367540 > LCK4953 Low-Voltage PLL Clock Driver PDF資料下載

參數(shù)資料

| 型號: | LCK4953 |

| 英文描述: | Low-Voltage PLL Clock Driver |

| 中文描述: | 低電壓PLL時鐘驅動器 |

| 文件頁數(shù): | 3/6頁 |

| 文件大小: | 98K |

| 代理商: | LCK4953 |

Agere Systems Inc.

3

Data Sheet

November 2001

Low-Voltage PLL Clock Driver

LCK4953

Absolute Maximum Ratings

(continued)

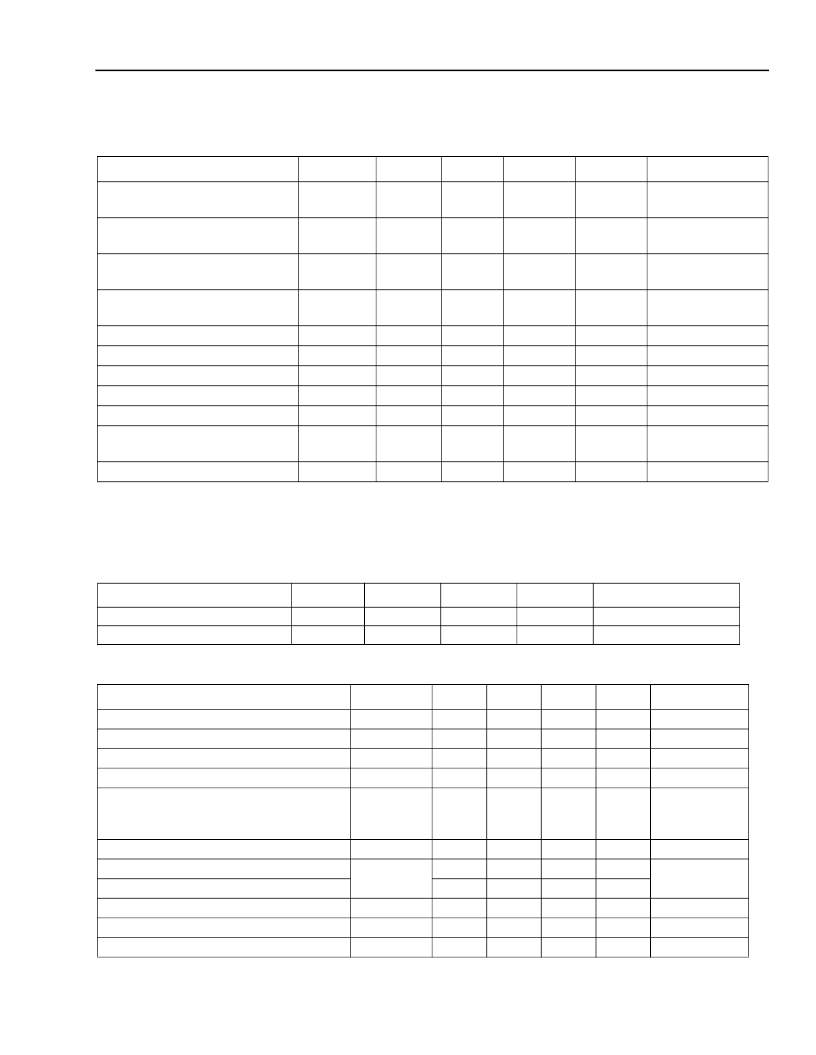

Table 3. dc Characteristics

(T

A

= 0

°

C to 70

°

C, V

DD

= 3.3 V

±

5%)

Table 4. PLL Input Reference Characteristics

(T

A

= 0

°

C to 70

°

C)

Table 5. ac Characteristics

(T

A

= 0

°

C to 70

°

C, V

DD

= 3.3 V

±

5%)

Parameter

Symbol

Min

Typ

Max

Unit

Condition

Input High-voltage LVCMOS

Inputs

Input Low-voltage LVCMOS

Inputs

Peak-to-peak Input Voltage

PECL_CLK

Common-mode Range

PECL_CLK

Output High Voltage

Output Low Voltage

Input Current

Input Capacitance

Power Dissipation Capacitance

Maximum Quiescent Supply

Current Non-PLL

Maximum PLL Supply Current

V

IH

2.0

—

3.6

V

—

V

IL

—

—

0.8

V

—

Vp-p

300

—

1000

mV

—

V

CMR

V

DD

–

1.5

—

V

DD

–

0.6

mV

—

*

*

V

CMR

is the difference from the most positive side of the differential input signal. Normal operation is obtained when the high input is within

the V

CMR

range and the input swing lies within the Vp-p specification.

The LCK4953 outputs can drive series- or parallel-terminated 50

(or 50

to V

CC

/2) transmission lines on the incident edge.

Total Power = (I

DDPLL

+ I

DDQ

+ fCV) * V; where f = fref, V = V

DDD

, C = total load capacitance on all outputs.

V

OH

V

OL

I

IN

C

IN

Cpd

I

DDQ

2.4

—

—

—

—

—

—

—

—

—

12

—

—

0.6

±

120

4

—

1

V

V

μ

A

pF

pF

mA

I

OH

=

–

30 mA

I

OL

= 30 mA

—

—

Per output

All V

DD

pins except

V

DD

A

V

DD

A pin only

I

DDPLL

—

—

45

mA

Parameter

Symbol

fref

trefdc

Min

25

25

Max

130

75

Unit

MHz

%

Condition

—

—

Reference Input Frequency

Reference Input Duty Cycle

Parameter

Symbol

tr, tf

tpw

tsk(O)

fV

CO

fout

Min

0.10

47

—

200

25

50

—

–

75

3

Typ

—

50

—

—

—

—

—

—

—

Max

1.0

53

75

520

65

130

250

125

7

1.5

7

6

50

Unit

ns

%

ps

MHz

MHz

MHz

MHz

ps

ns

Condition

0.8 V to 2.0 V

—

—

—

VCOSEL = 1

VCOSEL = 0

—

tref = 75 MHz

PLL bypassed

Output Rise/Fall Time

Output Duty Cycle

Output-to-output Skews

PLL V

CO

Lock Range

Frequency Output:

Frequency PLL

Bypass Mode

Input to Ext_FB Delay (with PLL locked)

Input to Q Delay

Part to Part Delay

Output Disable Time

Output Enable Time

Cycle-to-cycle Jitter (peak-to-peak)

tpd (lock)

tpd(bypass)

tPLZHZ

tPZL

tjitter

—

—

—

—

—

—

ns

ns

ps

—

—

fout > 75 MHz

相關PDF資料 |

PDF描述 |

|---|---|

| LCS2W123.3W10 | Analog IC |

| LCS2W1233-10W | Analog IC |

| LCS2W243.3W10 | Analog IC |

| LCS2W2433-10W | Analog IC |

| LCS2W483.3W10 | Analog IC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LCK4972 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Voltage PLL Clock Driver |

| LCK4973 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Voltage PLL Clock Driver |

| LCK4993 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Voltage PLL Clock Drivers |

| LCK4993KB-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Voltage PLL Clock Drivers |

| LCK4993KB-DT | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Voltage PLL Clock Drivers |

發(fā)布緊急采購,3分鐘左右您將得到回復。