- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358795 > LH521028 (Sharp Corporation) CMOS 64K x 18 Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | LH521028 |

| 廠商: | Sharp Corporation |

| 英文描述: | CMOS 64K x 18 Static RAM |

| 中文描述: | 64K的× 18的CMOS靜態(tài)RAM |

| 文件頁(yè)數(shù): | 7/15頁(yè) |

| 文件大?。?/td> | 153K |

| 代理商: | LH521028 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

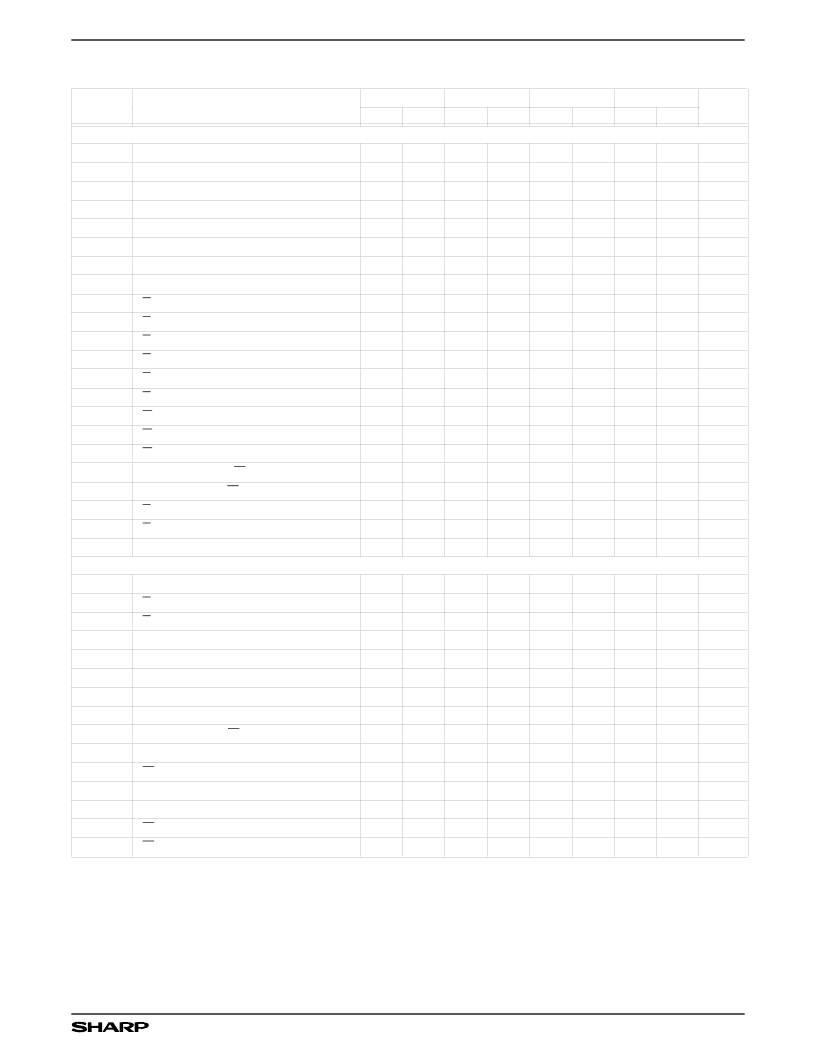

AC ELECTRICAL CHARACTERISTICS

1

(Over Operating Range)

SYMBOL

DESCRIPTION

–17

–20

–25

–35

UNITS

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

READ CYCLE

17

t

RC

t

AA

t

ASL

t

AHL

t

LEA

t

LHM

t

OH

t

LH

t

EA

t

ELZ

t

EHZ

t

SA

t

SLZ

t

SHZ

t

GA

t

GLZ

t

GHZ

t

RCS

t

RCH

t

PU

t

PD

t

WA

Read Cycle Timing

Address Access Time

Address Setup to Latch Enable

Address Hold from Latch Enable

Latch Enable to Data Valid

Latch Enable High Pulse Width

Output Hold from Address Change

Output Hold from Latch High

E Low to Valid Data

E Low to Output Active

2,3

E High to Output High-Z

2,3

S Low to Valid Data

S Low to Output Active

2,3

S High to Output High-Z

2,3

G Low to Valid Data

G Low to Output Active

2,3

G High to Output High-Z

2,3

Read Setup from W High

Read Hold from W Low

E LOW to Power Up Time

3

E HIGH to Power Down Time

3

Access Time From Write Enable HIGH

20

25

35

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

17

20

25

35

3

4

3

5

3

6

3

6

19

22

27

37

5

3

4

5

5

7

6

5

7

6

5

7

17

20

25

35

3

3

3

3

10

9

10

10

12

12

20

20

2

2

3

3

10

8

10

9

12

12

20

20

0

0

0

0

8

8

10

20

0

0

0

0

0

0

0

0

0

0

0

0

17

20

20

25

25

28

35

35

WRITE CYCLE

17

13

13

13

0

0

3

4

0

5

13

9

0

t

WC

t

EW

t

SW

t

AW

t

AS

t

AH

t

ASL

t

AHL

t

LHW

t

LHM

t

WP

t

DW

t

DH

t

WHZ

t

WLZ

Write Cycle Time

E Low to End of Write

S LOW to End of Write

Address Valid to End of Write

Address Setup to Start of Write

Address Hold from End of Write

Address Setup to Latch Enable

Address Hold from Latch Enable

Latch Hold from W High

Latch Enable HIGH Pulse Width

W Pulse Width

Input Data Setup Time

Input Data Hold Time

W Low to Output High-Z

2,3

W High to Output Active

2,3

20

15

15

15

0

0

3

5

0

5

15

12

0

25

20

20

20

0

0

3

6

0

6

20

13

0

35

30

30

30

0

0

3

6

0

6

30

15

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

8

8

10

14

3

3

3

3

NOTES:

1.

AC Electrical Characteristics specified at ‘AC Test Conditions’ levels.

2.

Active output to High-Z and High-Z to output active tests specified for a

±

500 mV transition from steady state levels into the test load.

C

Load

= 5 pF.

3.

Guaranteed but not tested.

CMOS 64K

×

18 Static RAM

LH521028

4-217

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH52253K35 | CMOS 64K X 4 STATIC RAM |

| LH52256C-10LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

| LH52256CD-70LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

| LH52256CHN-70LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

| LH52256CHN-85LL | 256K SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH521028A | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:CMOS 64K x 18 Static RAM |

| LH521028AU-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。