- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358799 > LH5PV8512 (Sharp Corporation) CMOS 4M (512K x 8) Pseudo-Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | LH5PV8512 |

| 廠商: | Sharp Corporation |

| 英文描述: | CMOS 4M (512K x 8) Pseudo-Static RAM |

| 中文描述: | 的CMOS 4分(為512k × 8)偽靜態(tài)存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 6/12頁(yè) |

| 文件大?。?/td> | 90K |

| 代理商: | LH5PV8512 |

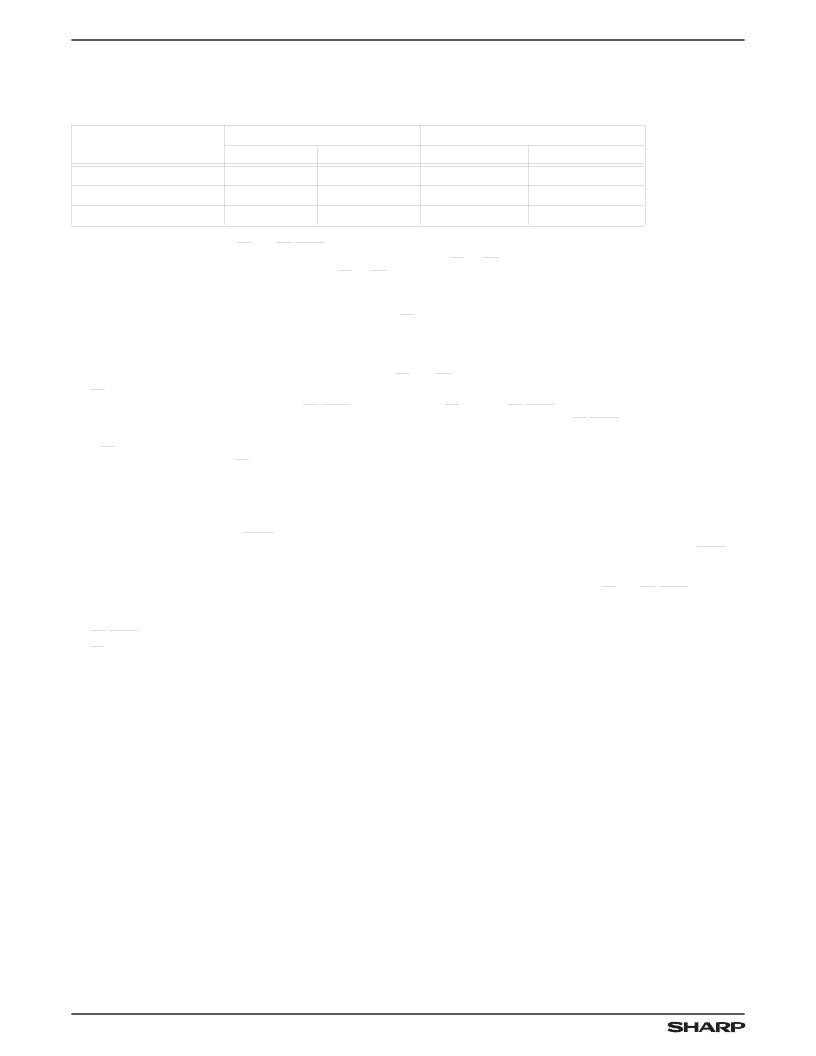

NOTES:

1.

AC characteristics are measured at t

T

= 2 ns.

2.

AC characteristics are measured at the following condition:

INPUT VOLTAGE

OUTPUT VOLTAGE

V

IH

V

IL

V

OH

V

OL

Input level

Input reference level

Output reference level

2.4 V

1.4 V

0.4 V

1.4 V

2.0 V

0.8 V

3.

4.

In order to initialize the circuit, CE and OE/RFSH should be kept V

IH

for 100

μ

s after power-up and followed by at least 8 dummy cycles.

If input signals of opposite phase to the outputs are applied in write cycle, OE or WE must disable output buffer proir to applying data to

the device and data inputs must be floating prior to OE or WE turning on outputs buffer.

Because a PSRAM operates dynamically like a DRAM, it is recommended to put bypass capacitors between V

CC

and GND to absorb power

supply noise due to the peak current.

Address signals are latched in the memory at the falling edge of CE.

Measured with a load equivalent to 50 pF.

t

, t

, t

, t

, t

, and t

are sampled, and not 100% tested. t

, t

OHZ

, and t

WHZ

define the time at which the output achieves

the open circuit condition and they are not referenced to output voltage levels.

Input data is latched in the memory at the earlier rising edge of CE and WE.

10. CE only refresh or auto-refresh is needed to be executed 2,048 times within 32 ms.

11. Auto-refresh and self-refresh are defined by OE/RFSH pulse width during CE = V

IH

. If OE/RFSH pulse width is shorter than t

FAP

(MAX.),

the cycle is an auto-refresh cycle and memory cells are refreshed by an internal address counter. If OE/RFSH pulse width is longer than

t

FAS

(MIN.), the cycle is a self-refresh cycle and memory cells are refreshed by an internal clock generator automatically.

12. If CE only refresh is used during normal read/write cycles, the first address refresh must be started within 15

μ

s after self-refresh or data

retention mode ends, and the CE only refresh must be executed continuously for 2,048 refresh cycles.

13. If distributed auto-refresh is used during normal read/write cycles, the first auto-refresh must be started within 15

μ

s after self-refresh or

data retention mode ends.

14. If burst auto-refresh is used during normal read/write cycles, the first auto-refresh must be started within 15

μ

s after self-refresh or data

retention mode ends, and the auto-refresh must be executed continuously for 2,048 refresh cycles.

15. After 8,000 ns (t

FAP

(MAX.)) from RFSH falling, the memory resets its internal address counter and enters self-refresh cycle. At the beginning

of the self-refresh cycle, it takes longer than 8 ms (t

FAS

(MIN.)) for all addresses to be refreshed. Therefore, in case that the RFSH = L

pulse length is from 8,000 ns to 8 ms, refresh all addresses by external clocks within 32 ms before the self-refresh to keep refresh time

interval (t

REF

).

16. After self-refresh cycle or data retention mode ends, t

FRS

(MIN.) is necessary to reset the refresh operation. CE and OE/RFSH should kept

V

IH

for t

FRS

(MIN.).

17. The data retention period is longer than t

FAS

(MIN.) like self-refresh cycle.

18. OE/RFSH must be lower than 0.2 V during the data retention period.

19. CE must be higher than V

CC

- 0.2 V during the data retention period.

20. The transition time of the supply voltage in data retention mode must be slower than 0.05 V/ms.

5.

6.

7.

8.

9.

LH5PV8512

CMOS 4M (512K

×

8) Pseudo-Static RAM

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH6V4256 | CMOS 1M (256K x 4) Dynamic RAM |

| LH75400 | System-on-Chip |

| LH77790B | Embedded Microcontroller(32位嵌入式微控制器) |

| LH79525 | 16/32-bit System-on-Chip with Color LCD Controller |

| LH7A400 | 32-Bit System-on-Chip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH5PV8512N-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Pseudo-Static RAM |

| LH-5S-1 | 制造商:Shinagawa Shoko 功能描述: |

| LH-5S-10 | 制造商:Shinagawa Shoko 功能描述: |

| LH-5S-12 | 制造商:Shinagawa Shoko 功能描述: |

| LH-5S-15 | 制造商:Shinagawa Shoko 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。