- 您現在的位置:買賣IC網 > PDF目錄10043 > LTC2207IUK-14#TRPBF (Linear Technology)IC ADC 14BIT 105MSPS 48-QFN PDF資料下載

參數資料

| 型號: | LTC2207IUK-14#TRPBF |

| 廠商: | Linear Technology |

| 文件頁數: | 16/32頁 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 105MSPS 48-QFN |

| 標準包裝: | 2,000 |

| 位數: | 14 |

| 采樣率(每秒): | 105M |

| 數據接口: | 并聯 |

| 轉換器數目: | 1 |

| 功率耗散(最大): | 1.07W |

| 電壓電源: | 單電源 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-WFQFN 裸露焊盤 |

| 供應商設備封裝: | 48-QFN-EP(7x7) |

| 包裝: | 帶卷 (TR) |

| 輸入數目和類型: | 1 個差分 |

| 配用: | DC890B-ND - BOARD USB DATA COLLECTION |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

LTC2207-14/LTC2206-14

23

220714614fc

LTC2207-14/LTC2206-14

2207614 F11

OVDD

VDD

0.1μF

TYPICAL

DATA

OUTPUT

OGND

OVDD

0.5V

TO 3.6V

PREDRIVER

LOGIC

DATA

FROM

LATCH

33Ω

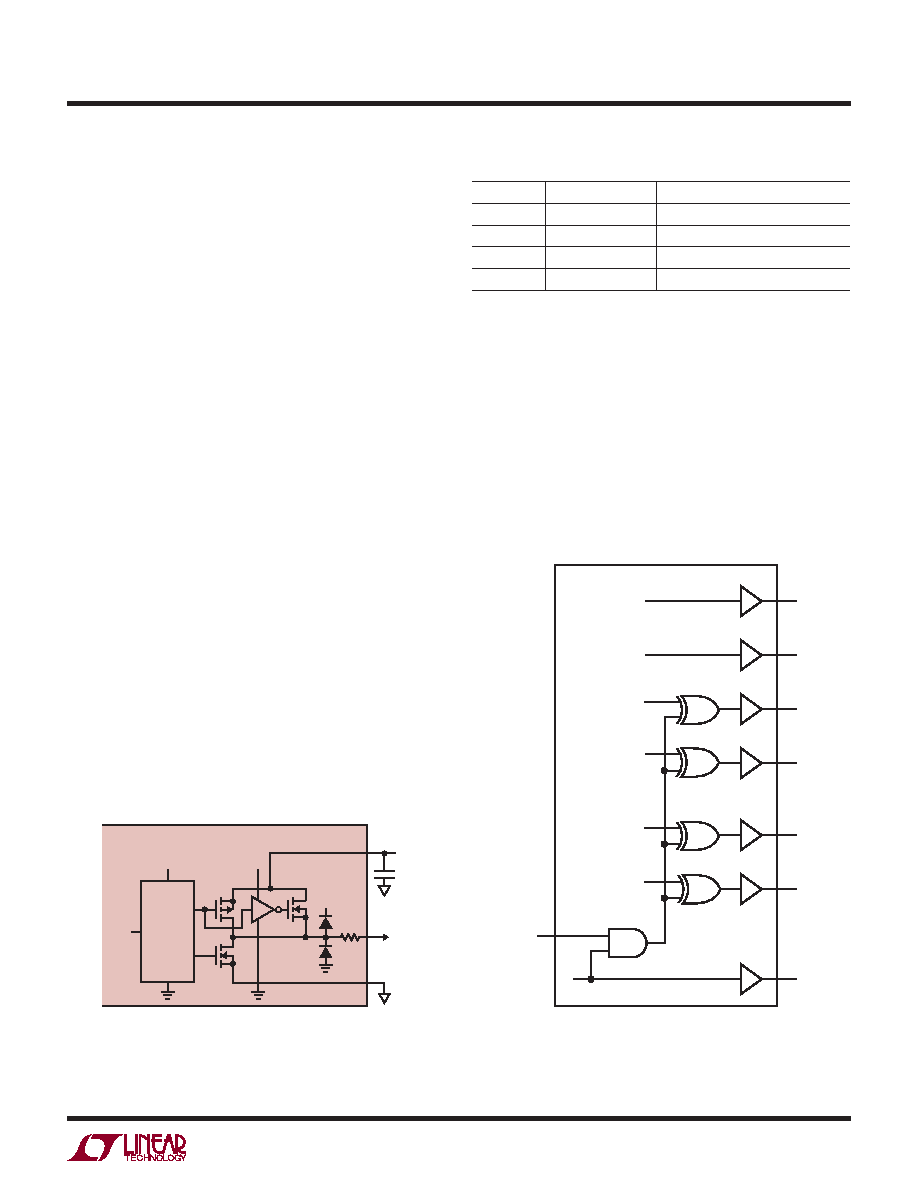

Figure 11. Equivalent Circuit for a Digital Output Buffer

DIGITAL OUTPUTS

Digital Output Buffers

Figure 11 shows an equivalent circuit for a single output

buffer. Each buffer is powered by OVDD and OGND, isolated

from the ADC power and ground. The additional N-channel

transistor in the output driver allows operation down to

low voltages. The internal resistor in series with the output

eliminates the need for external damping resistors.

As with all high speed/high resolution converters, the

digital output loading can affect the performance. The

digital outputs of the LTC2207-14/LTC2206-14 should drive

a minimum capacitive load to avoid possible interaction

between the digital outputs and sensitive input circuitry.

The output should be buffered with a device such as a

ALVCH16373 CMOS latch. For full speed operation the

capacitive load should be kept under 10pF. A resistor in

series with the output may be used but is not required since

the output buffer has a series resistor of 33

Ω on chip.

Lower OVDD voltages will also help reduce interference

from the digital outputs.

Data Format

The LTC2207-14/LTC2206-14 parallel digital output can

be selected for offset binary or 2’s complement format.

The format is selected with the MODE pin. This pin has a

four level logic input, centered at 0, 1/3VDD, 2/3VDD and

VDD. An external resistor divider can be used to set the

1/3VDD and 2/3VDD logic levels. Table 1 shows the logic

states for the MODE pin.

Table 1. MODE Pin Function

MODE

OUTPUT FORMAT

CLOCK DUTY CYCLE STABILIZER

0(GND)

Offset Binary

Off

1/3VDD

Offset Binary

On

2/3VDD

2’s Complement

On

VDD

2’s Complement

Off

Overow Bit

An overow output bit (OF) indicates when the converter

is over-ranged or under-ranged. A logic high on the OF

pin indicates an overow or underow.

Output Clock

The ADC has a delayed version of the encode input available

as a digital output. Both a noninverted version, CLKOUT+

and an inverted version CLKOUT– are provided. The

CLKOUT+/CLKOUT– can be used to synchronize the

Figure 12. Functional Equivalent of Digital Output Randomizer

CLKOUT+

OF

D13/D0

D12/D0

D2/D0

D1/D0

D0

D1

RAND = HIGH,

SCRAMBLE

ENABLED

D2

D12

D13

OF

LTC2207-14/LTC2206-14

CLKOUT

RAND

2207614 F12

APPLICATIONS INFORMATION

相關PDF資料 |

PDF描述 |

|---|---|

| MS3108E20-11P | CONN PLUG 13POS RT ANG W/PINS |

| IDT72811L15TF | IC FIFO SYNC DUAL 512X9 64QFP |

| VI-2VX-MY | CONVERTER MOD DC/DC 5.2V 50W |

| LT1134AIN#PBF | IC 4DRV/4RCV RS232 5V 24-DIP |

| AD774BKN | IC ADC 12BIT W/BUFF REF 28-DIP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LTC2207UK | 制造商:LINER 制造商全稱:Linear Technology 功能描述:16-Bit, 105Msps/80Msps ADCs |

| LTC2207UK-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:14-Bit, 105Msps/80Msps ADCs |

| LTC2208 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Dual 14-Bit 250Msps |

| LTC2208-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:14-Bit, 130Msps ADC |

| LTC2208CUP | 制造商:Linear Technology 功能描述:IC ADC 16BIT 130MSPS 64-QFN |

發(fā)布緊急采購,3分鐘左右您將得到回復。