- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367612 > LU6612 LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX PDF資料下載

參數(shù)資料

| 型號(hào): | LU6612 |

| 英文描述: | LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| 中文描述: | LU6612 FASTCAT商標(biāo)單的10BASE-T/100BASE-TX快速以太網(wǎng)場(chǎng)效應(yīng)管 |

| 文件頁數(shù): | 9/36頁 |

| 文件大?。?/td> | 528K |

| 代理商: | LU6612 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

Lucent Technologies Inc.

9

Data Sheet

July 2000

LU6612

FASTCAT Single-FET for 10Base-T/100Base-TX

Pin Information

(continued)

Pin Descriptions

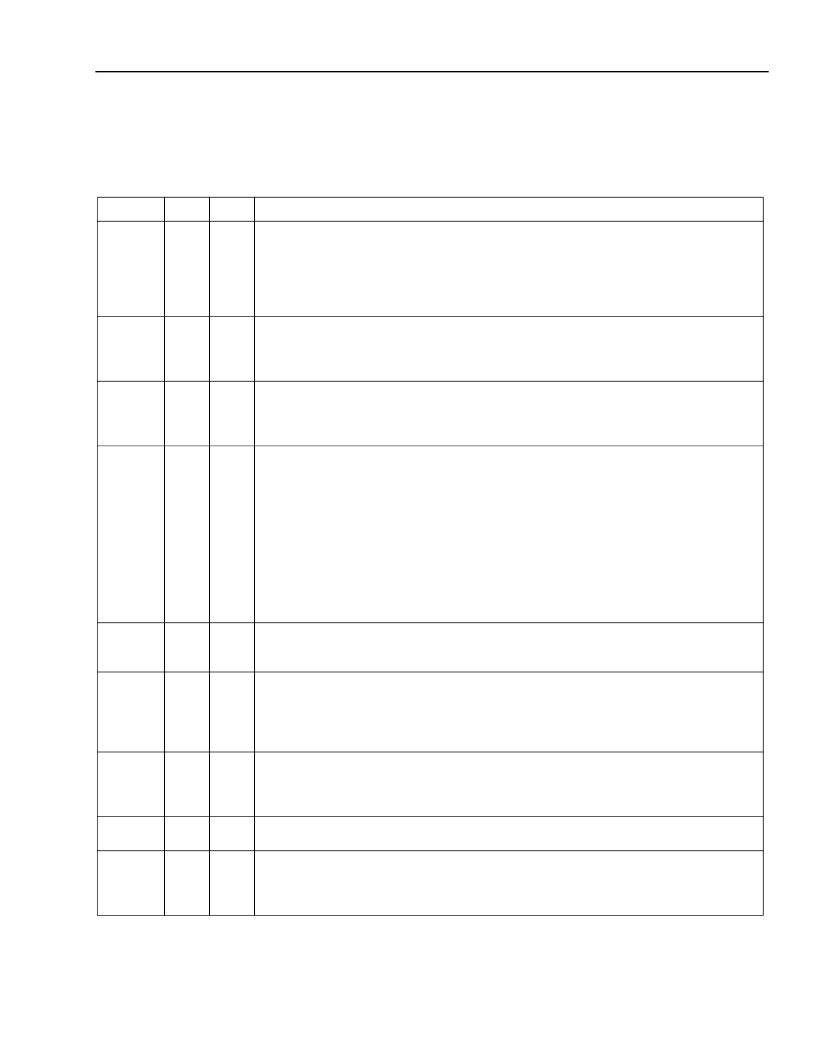

Table 1. MII/Serial Interface Pins (17)

Signal

COL

Type

O

Pin

43

Description

Collision Detect.

This signal signifies in half-duplex mode that a collision has

occurred on the network. COL is asserted high whenever there is transmit and

receive activity on the UTP media. COL is the logical AND of TX_EN and receive

activity, and is an asynchronous output. When SERIAL_SEL (register 30, bit 1) is high

and in 10Base-T mode, this signal indicates the jabber timer has expired. This signal

is held low in full-duplex mode.

Carrier Sense.

When CRS_SEL (register 29, bit 10) is low, CRS is asserted high

when either the transmit or receive is nonidle. This signal remains asserted through-

out a collision condition. When CRS_SEL (register 29, bit 10) is high, CRS is

asserted on receive activity only.

Receive Clock.

25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in

10 Mbits/s nibble mode, 10 MHz in 10 Mbits/s serial mode. RX_CLK has a worst-case

45/55 duty cycle. RX_CLK provides the timing reference for the transfer of RX_DV,

RXD, and RX_ER signals.

37:40

Receive Data.

4-bit parallel data outputs that are synchronous to the falling edge of

RX_CLK. When RX_ER is asserted high in 100 Mbits/s mode, an error code will be

presented on RXD[3:0] where appropriate. The codes are as follows:

I

Packet errors: ERROR_CODES = 2h;

I

Link errors: ERROR_CODES = 3h (Packet and link error codes will only be

repeated if registers [29.9] and [29.8] are enabled.);

I

Premature end errors: ERROR_CODES = 4h;

I

Code errors: ERROR_CODES = 5h.

When SERIAL_SEL (register 30, bit 1) is active-high and 10 Mbits/s mode is selected,

RXD[0] is used for data output and RXD[3:1] are 3-stated.

45

Receive Data Valid.

When this pin is high, it indicates the LU6612 is recovering and

decoding valid nibbles on RXD[3:0], and the data is synchronous with RX_CLK.

RX_DV is synchronous with RX_CLK. This pin is not used in serial 10 Mbits/s mode.

46

Receive Error.

When high, RX_ER indicates the LU6612 has detected a coding error

in the frame presently being transferred. RX_ER is synchronous with RX_CLK. When

the encode/decode bypass (EDB) is selected through the MII management interface,

this output serves as the RXD[4] output. This pin is only valid when LU6612 is in

100 Mbits/s mode.

47

Transmit Clock.

25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in

10 Mbits/s MII mode, 10 MHz output in 10 Mbits/s serial mode. TX_CLK provides tim-

ing reference for the transfer of the TX_EN, TXD, and TX_ER signals. These signals

are sampled on the rising edge of TX_CLK.

31:34

Transmit Data.

4-bit parallel input synchronous with TX_CLK. When SERIAL_SEL

(register 30, bit 1) is active-high and 10 Mbits/s mode is selected, only TXD[0] is valid.

30

Transmit Enable.

When driven high, this signal indicates there is valid data on

TXD[3:0]. TX_EN is synchronous with TX_CLK. When SERIAL_SEL

(register 30, bit 1) is active-high and 10 Mbits/s mode is selected, this pin indicates

there is valid data on TXD[0].

CRS

O

42

RX_CLK

O

44

RXD[3:0]

O

RX_DV

O

RX_ER/

RXD[4]

O

TX_CLK

O

TXD[3:0]

I

TX_EN

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU6612-T64-DB | LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| LU6612 | Single-FET for 10Base-T/100Base-TX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX 的單快速以太網(wǎng)收發(fā)器) |

| LU6X14FT | Telecommunication IC |

| LU97 | Telecommunication IC |

| LUC3X01 | LAN Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU6612-T64-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| LU67 | 制造商:Thomas & Betts 功能描述:2 CONDUIT BODY,GRAY IRON,LU,F-7 |

| LU670Z | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:GREEN OVAL LAMP LED |

| LU671 | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:RED OVAL LAMP LED |

| LU680Z | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:GREEN OVAL LAMP LED |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。