- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45045 > M38268MCA-XXXGP 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | M38268MCA-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, LQFP-100 |

| 文件頁數(shù): | 93/95頁 |

| 文件大?。?/td> | 1006K |

| 代理商: | M38268MCA-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當(dāng)前第93頁第94頁第95頁

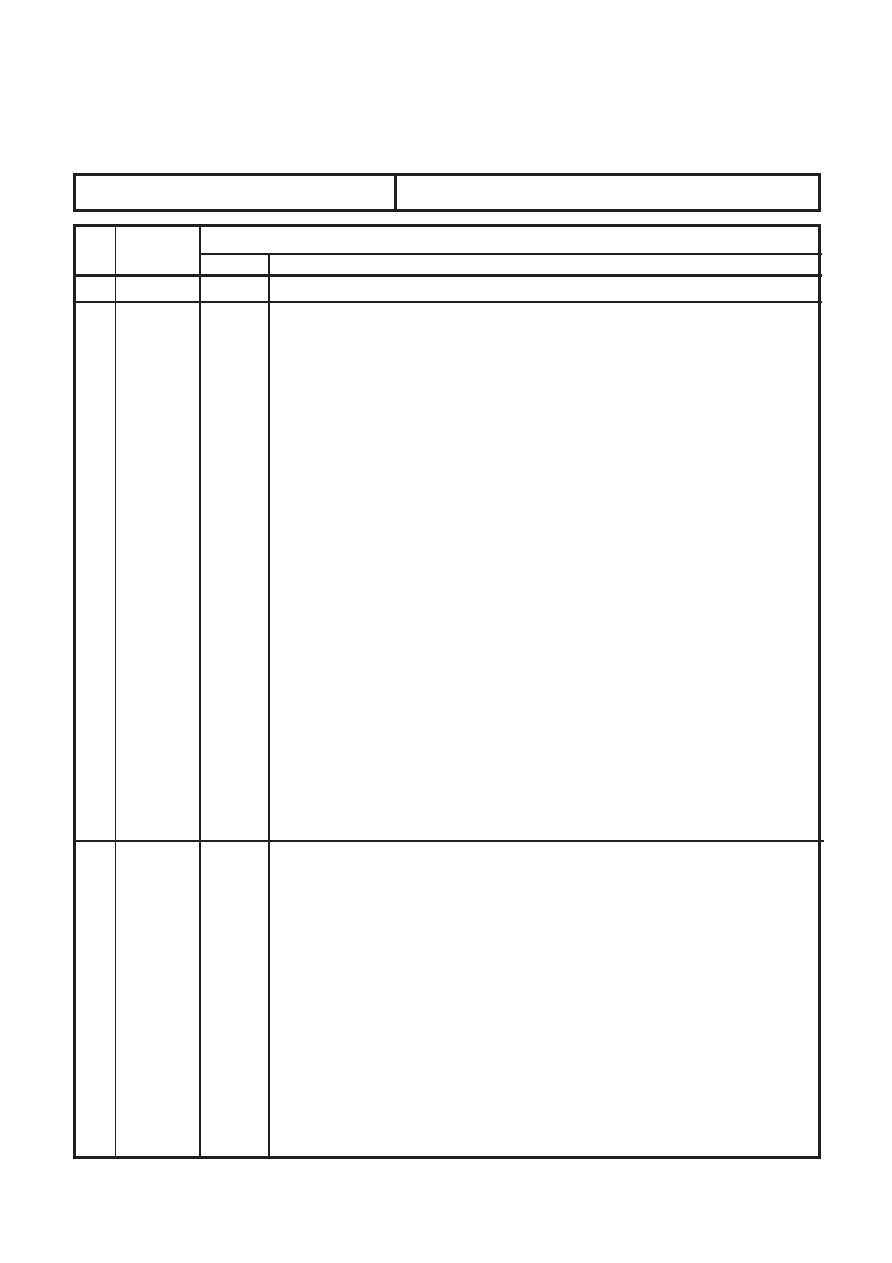

REVISION HISTORY

Rev.

Date

Description

Page

Summary

3826 Group (A version) Data Sheet

1.00 Feb. 18, 2003

1.02 Jul. 31, 2003

First edition issued

Power dissipation revised.

Table 1 Pin description (1) VCC VSS; Function description revised.

Fig.5 Memory expansion plan revised.

Fig.14 Port block diagram (1);

(4) Ports P16, P17,P2, P41, P42 and (5) Port P44 revised.

Fig.15 Port block diagram (2);

(7) Port P46 and (11) Port P54 revised.

Fig.16 Port block diagram (3);

(14) Port P55, (15) Ports P56, P57 and (17) Port P60 revised.

Fig.17 Port block diagram (4);

(19) Port P62 revised.

Fig.40 A-D converter block diagram

Voltage Multiplier (3 Times)

Description of order for operating the voltage multiplier revised.

ROM ORDERING METHOD revised.

Table 16 Recommended operating conditions (4); f(CNTR0) f(CNTR1) revised.

Table 18 Electrical characteristics (2); ICC revised.

Table 19 A-D converter characteristics (1); Note revised.

Table 20 A-D converter characteristics (2); Note revised.

Table 22 Timing requirements (1);

tc(SCLK), tWH(SCLK), tWL(SCLK), tsu(RxD-SCLK), th(SCLK-RxD); revised.

Table 23 Timing requirements (2);

tc(SCLK), tWH(SCLK), tWL(SCLK), tsu(RxD-SCLK), th(SCLK-RxD); revised.

Table 25 Switching characteristics (2) ; tr(SCLK1) tf(SCLK1) revised.

Package revised.

Word standardized: “A/D converter”, “D/A converter”, “Serial interface”

FEATURES: A/D converter revised. APPLICATIONS: “household appliances” added.

Fig. 4: Description of RAM added.

Fig. 5: Development status: “under development”

→ “mass production”

Table 3: Date revised.

SFR: AD conversion low-order register (ADL) added to address 001416 and AD

conversion high-order register (ADH) added to address 003516.

A/D CONVERTER: Description revised and ADL added to Fig. 38.

Fig. 39 added and Fig. 40 revised.

Fig. 58: AD conversion low-order register added.

Description revised. Fig. 59: Note added.

Fig. 61: Note 2 added.

Note on Power supply voltage added.

–

1

4

7

18

19

20

21

39

44

58

61

63

64

65

66

67

-

1

6

7

13

38

39

53

54

55

60

2.00 May.24, 2006

(1/2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M3826AMFA-XXXFP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| M3826AMFLXXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP100 |

| M38268MCLXXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP100 |

| M3826AMFLXXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP100 |

| M38279EFHP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3826AEFFP#U0 | 制造商:Renesas 功能描述:MCU 8-bit 740 CISC 60KB EPROM 5V 100-Pin PQFP Tray |

| M3826AMFA-221FP#U0 | 制造商:Renesas Electronics Corporation 功能描述: |

| M3826-BK001 | 制造商:Alpha Wire 功能描述: |

| M3826-BK002 | 制造商:Alpha Wire 功能描述: |

| M3826-BK005 | 制造商:Alpha Wire 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。