- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45045 > M3826AMFA-XXXGP 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | M3826AMFA-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, LQFP-100 |

| 文件頁數(shù): | 38/93頁 |

| 文件大小: | 996K |

| 代理商: | M3826AMFA-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

Rev.2.00

May. 24, 2006

page 43 of 90

REJ03B0028-0200

3826 Group (A version)

CTCSS Function

(Continuous Tone-Controlled Squelch

System)

The CTCSS function is used to generate the sine wave of single

frequency automatically. The CTCSS output waveform can be out-

put from DA2 pin. CTCSS waveform is outputted by setting “1” to

the CTCSS/DA2 output enable bit (bit 1 of address 003616), and

setting “1” to the CTCSS/DA2 selection bit (bit 3 of address

003616). In order to set the frequency of CTCSS output, value is

written in the CTCSS timer. The CTCSS timer consists of a 10-bit

timer. When writing a value to the CTCSS timer, write the low-or-

der byte first.

Rating frequency (Hz)

67.0

77.0

88.5

100.0

107.2

114.8

123.0

131.8

141.3

151.4

162.2

173.8

186.2

203.5

218.1

233.6

250.3

n (Timer value)

465

405

352

312

291

271

253

236

220

205

192

179

167

153

142

133

124

Error frequency (Hz)

0.06

–0.03

0.027

–0.16

–0.18

0.09

0.03

0.06

0.10

0.30

–0.28

–0.19

–0.58

0.43

–0.39

–0.30

Deviation (%)

0.089

–0.038

0.030

–0.160

–0.167

0.078

0.026

0.043

0.073

0.198

–0.174

–0.109

–0.101

–0.284

0.198

–0.167

–0.120

Output frequency (Hz)]

67.06

76.97

88.53

99.84

107.02

114.89

123.03

131.86

141.40

151.70

161.92

173.61

186.01

202.92

218.53

233.20

250.00

Table 10 Example of frequency accuracy (at f(XIN) = 4 MHz)

f (XIN)/2

(n+1) 64

Vcc

2

When reading a value from the CTCSS timer, read the high-order

byte first. By the value written in the CTCSS timer is n, the sine

wave of the following frequency is generated.

f =

(Hz)

Set “00616” or more to the CTCSS timer. “0016” is automatically

set to the high-order of the CTCSS timer and “0616” is automati-

cally set to the low-order of the CTCSS timer after reset release.

The amplitude of CTCSS output is obtained by the following for-

mula.

C =

If the D/A2 conversion register is read when the CTCSS function

is selected, the digital value of CTCSS output can be read.

Table 10 shows the example of frequency accuracy (at f(XIN) = 4

MHz).

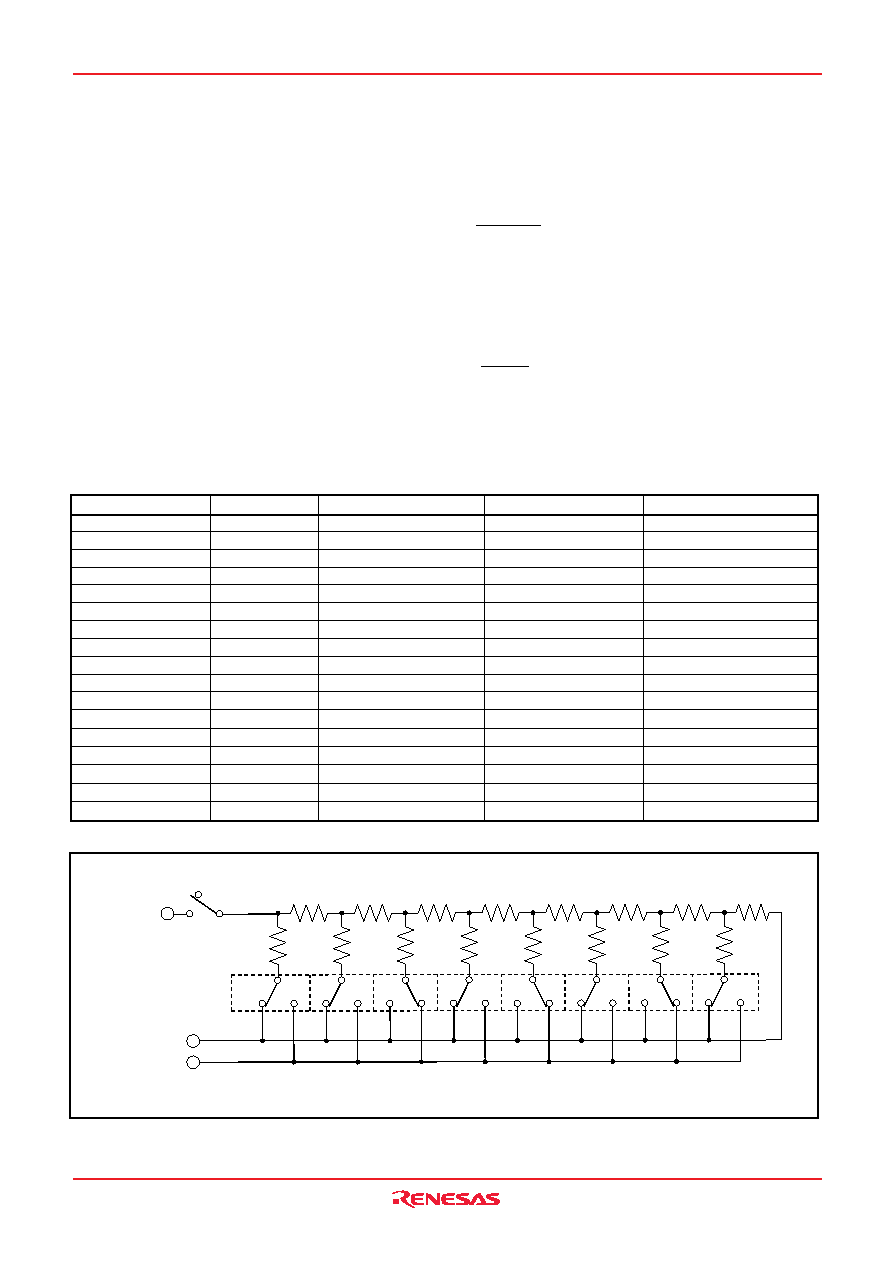

Fig. 45 Equivalent connection circuit of D/A converter

AVSS

VREF

“0”

“1”

MSB

“0”

“1”

R

2R

R

2R

R

2R

R

2R

R

2R

R

2R

R

2R

LSB

2R

DAi

DAi conversion register

DAi output enable bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M3826AMFA-XXXGP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| M38268MCA-XXXGP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| M3826AMFA-XXXFP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP100 |

| M3826AMFLXXXGP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP100 |

| M38268MCLXXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3826-BK001 | 制造商:Alpha Wire 功能描述: |

| M3826-BK002 | 制造商:Alpha Wire 功能描述: |

| M3826-BK005 | 制造商:Alpha Wire 功能描述: |

| M3826-BK199 | 制造商:Alpha Wire 功能描述: |

| M3826-BLACK-100 | 制造商:Alpha Wire 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。