- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377830 > M52D128168A-7.5TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 2M x 16 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M52D128168A-7.5TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 8M X 16 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| 封裝: | 0.400 INCH, LEAD FREE, TSOP2-54 |

| 文件頁數(shù): | 27/47頁 |

| 文件大小: | 1209K |

| 代理商: | M52D128168A-7.5TG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

ES MT

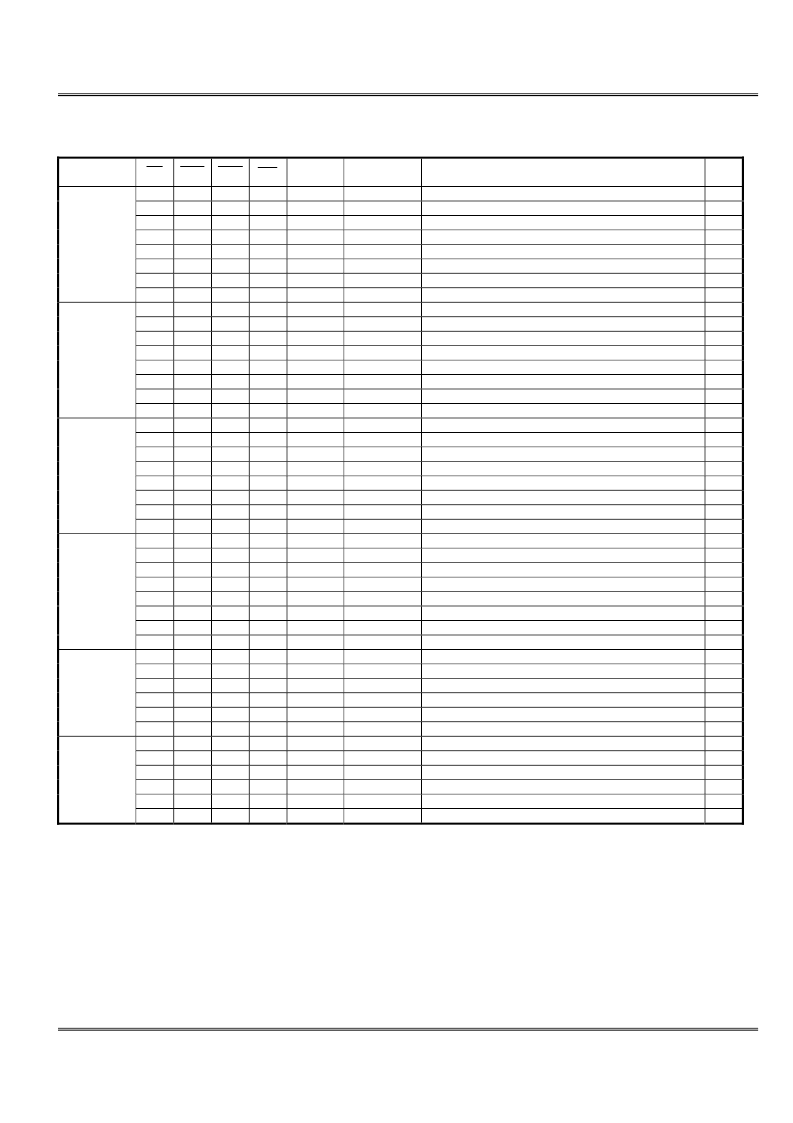

FUNCTION TURTH TABLE (TABLE 1)

Preliminary

M52D128168A

Elite Semiconductor Memory Technology Inc.

Revision

:

1.0

Publication Date

:

May. 2007

27/47

Current

State

IDLE

Row

Active

Read

Write

Read with

Auto

Precharge

Write with

Auto

Precharge

CS

H

L

L

L

L

L

L

L

H

L

L

L

L

L

L

L

H

L

L

L

L

L

L

L

H

L

L

L

L

L

L

L

H

L

L

L

L

L

H

L

L

L

L

L

RAS CAS

X

H

H

H

L

L

L

L

X

H

H

H

H

L

L

L

X

H

H

H

H

L

L

L

X

H

H

H

H

L

L

L

X

H

H

H

L

L

X

H

H

H

L

L

WE

X

H

L

X

H

L

H

L

X

H

L

H

L

H

L

X

X

H

L

H

L

H

L

X

X

H

L

H

L

H

L

X

X

H

L

X

X

X

X

H

L

X

X

X

BA

ADDR

ACTION

Note

X

H

H

L

H

H

L

L

X

H

H

L

L

H

H

L

X

H

H

L

L

H

H

L

X

H

H

L

L

H

H

L

X

H

H

L

H

L

X

H

H

L

H

L

X

X

X

BA

BA

BA

X

X

X

X

NOP

NOP

ILLEGAL

2

2

4

5

5

2

2

3

2

3

3

2

3

2

2

CA, A10/AP ILLEGAL

RA

A10/AP

X

OP code

X

X

X

CA, A10/AP Begin Read ; latch CA ; determine AP

CA, A10/AP Begin Write ; latch CA ; determine AP

RA

ILLEGAL

A10/AP

Precharge

X

ILLEGAL

X

NOP (Continue Burst to End

Row Active)

X

NOP (Continue Burst to End

Row Active)

X

Term burst

Row active

CA, A10/AP Term burst, New Read, Determine AP

CA, A10/AP Term burst, New Write, Determine AP

RA

ILLEGAL

A10/AP

Term burst, Precharge timing for Reads

X

ILLEGAL

X

NOP (Continue Burst to End

Row Active)

X

NOP (Continue Burst to End

Row Active)

X

Term burst

Row active

CA, A10/AP Term burst, New Read, Determine AP

CA, A10/AP Term burst, New Write, Determine AP

RA

ILLEGAL

A10/AP

Term burst, Precharge timing for Writes

X

ILLEGAL

X

NOP (Continue Burst to End

Row Active)

X

NOP (Continue Burst to End

Row Active)

X

ILLEGAL

CA, A10/AP ILLEGAL

RA, RA10

ILLEGAL

X

ILLEGAL

X

NOP (Continue Burst to End

Row Active)

X

NOP (Continue Burst to End

Row Active)

X

ILLEGAL

CA, A10/AP ILLEGAL

RA, RA10

ILLEGAL

X

ILLEGAL

Row (&Bank) Active ; Latch RA

NOP

Auto Refresh or Self Refresh

Mode Register Access

NOP

NOP

ILLEGAL

OP code

X

X

X

BA

BA

BA

BA

X

X

X

X

BA

BA

BA

BA

X

X

X

X

BA

BA

BA

BA

X

X

X

X

BA

BA

X

X

X

X

BA

BA

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M52D16161A | 512K x 16Bit x 2Banks Synchronous DRAM |

| M52D16161A-10BG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M52D16161A-10TG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M52D32162A | 1M x 16Bit x 2Banks Synchronous DRAM |

| M52D32162A-10BG | 1M x 16Bit x 2Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M52D128168A-7BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Mobile Synchronous DRAM |

| M52D128168A-7TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Mobile Synchronous DRAM |

| M52D16161A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 16Bit x 2Banks Mobile Synchronous DRAM |

| M52D16161A_09 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 16Bit x 2Banks Mobile Synchronous DRAM |

| M52D16161A_1 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 16Bit x 2Banks Mobile Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。