- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180232 > M58BW016BB90ZA6 (STMICROELECTRONICS) 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 PDF資料下載

參數(shù)資料

| 型號(hào): | M58BW016BB90ZA6 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 |

| 封裝: | 10 X 12 MM, 1 MM PITCH, LBGA-80 |

| 文件頁(yè)數(shù): | 35/63頁(yè) |

| 文件大?。?/td> | 895K |

| 代理商: | M58BW016BB90ZA6 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)

40/63

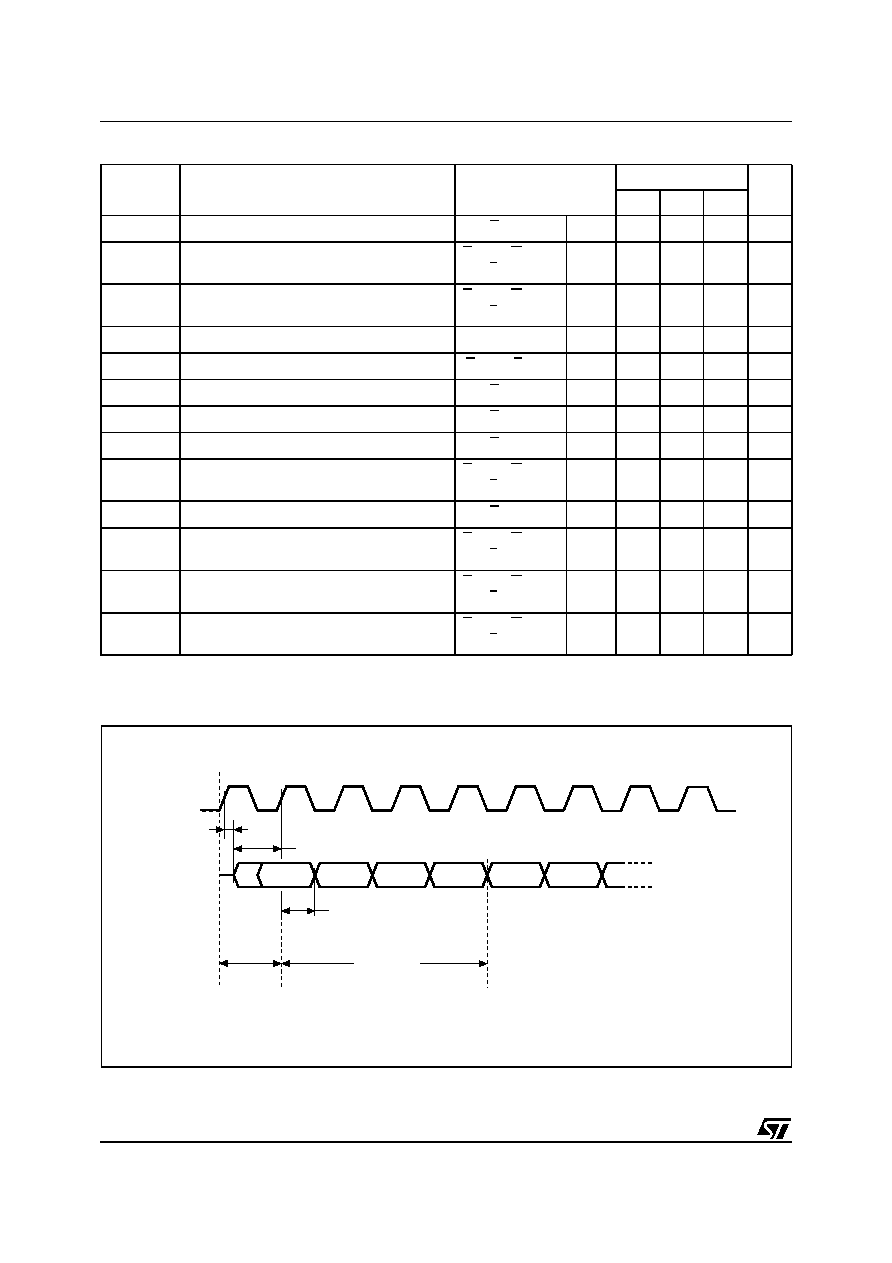

Table 20. Synchronous Burst Read AC Characteristics

Note: 1. Data output should be read on the valid clock edge.

2. For other timings see Table 16, Asynchronous Bus Read Characteristics.

Figure 15. Synchronous Burst Read (Data Valid from ’n’ Clock Rising Edge)

Note: For set up signals and timings see Synchronous Burst Read.

Symbol

Parameter

Test Condition

M58BW016

Unit

80

90

100

tAVLL

Address Valid to Latch Enable Low

E = VIL

Min

0

ns

tBHKH

Burst Address Advance High to Valid Clock

Edge

E = VIL, G = VIL,

L = VIH

Min

8

ns

tBLKH

Burst Address Advance Low to Valid Clock

Edge

E = VIL, G = VIL,

L = VIH

Min

8

ns

tELLL

Chip Enable Low to Latch Enable low

Min

0

ns

tGLQV

Output Enable Low to Output Valid

E = VIL, L = VIH

Min

25

ns

tKHAX

Valid Clock Edge to Address Transition

E = VIL

Min

5

ns

tKHLL

Valid Clock Edge to Latch Enable Low

E = VIL

Min

0

ns

tKHLX

Valid Clock Edge to Latch Enable Transition

E = VIL

Min

0

ns

tKHQX

Valid Clock Edge to Output Transition

E = VIL, G = VIL,

L = VIH

Min

3

ns

tLLKH

Latch Enable Low to Valid Clock Edge

E = VIL

Min

6

ns

tQVKH

(1)

Output Valid to Valid Clock Edge

E = VIL, G = VIL,

L = VIH

Min

6

ns

tRLKH

Valid Data Ready Low to Valid Clock Edge

E = VIL, G = VIL,

L = VIH

Min

6

ns

tKHQV

Valid Clock Edge to Output Valid

E = VIL, G = VIL,

L = VIH

Max

11

ns

AI04408b

K

n+5

n+4

n+3

n+2

n+1

n

DQ0-DQ31

tQVKH

tKHQX

Q0

Q1

Q2

Q3

Q4

Q5

SETUP

Burst Read

Q0 to Q3

tKHQV

Note: n depends on Burst X-Latency

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M58BW016BT90ZA6 | 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 |

| M58LR128FB95ZB6E | 8M X 16 FLASH 1.8V PROM, 95 ns, PBGA56 |

| M58LW128A150N1 | 8M X 16 FLASH 3V PROM, 150 ns, PDSO56 |

| M58WR064HU70ZB6U | 4M X 16 FLASH 1.8V PROM, 70 ns, PBGA44 |

| M59DR032F100N1T | 2M X 16 FLASH 1.8V PROM, 100 ns, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M58BW016BB90ZA6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BBT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BBZA | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BT100T3T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。