- 您現(xiàn)在的位置:買賣IC網 > PDF目錄180232 > M58BW016BB90ZA6 (STMICROELECTRONICS) 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 PDF資料下載

參數(shù)資料

| 型號: | M58BW016BB90ZA6 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 |

| 封裝: | 10 X 12 MM, 1 MM PITCH, LBGA-80 |

| 文件頁數(shù): | 8/63頁 |

| 文件大小: | 895K |

| 代理商: | M58BW016BB90ZA6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

16/63

the Address Inputs and pulsing Latch Enable Low,

VIL. The Address Inputs are latched by the Com-

mand Interface on the rising edge of Latch Enable,

Write Enable or Chip Enable, whichever occurs

first. Commands and Input Data are latched on the

rising edge of Chip Enable, E, or Write Enable, W,

whichever occurs first. Output Enable must remain

High, and Output Disable Low, during the whole

Asynchronous Bus Write operation.

See Figure 13, Asynchronous Latch Controlled

Write AC Waveforms, and Table 19, Asynchro-

nous Write and Latch Controlled Write AC Charac-

teristics, for details of the timing requirements.

Output Disable. The data outputs are high im-

pedance when the Output Enable, G, is at VIH or

Output Disable, GD, is at VIL.

Standby. When Chip Enable is High, VIH, and the

Program/Erase Controller is idle, the memory en-

ters Standby mode, the power consumption is re-

duced to the standby level and the Data Inputs/

Outputs pins are placed in the high impedance

state regardless of Output Enable, Write Enable or

Output Disable inputs.

Automatic Low Power. If there is no change in

the state of the bus for a short period of time during

Asynchronous Bus Read operations the memory

enters Auto Low Power mode where the internal

Supply Current is reduced to the Auto-Standby

Supply Current. The Data Inputs/Outputs will still

output data if a Bus Read operation is in progress.

Automatic Low Power is only available in Asyn-

chronous Read modes.

Power-Down. The memory is in Power-down

when Reset/Power-Down, RP, is at VIL. The pow-

er consumption is reduced to the power-down lev-

el

and

the

outputs

are

high

impedance,

independent of the Chip Enable, E, Output Enable,

G, Output Disable, GD, or Write Enable, W, inputs.

Electronic Signature. Two codes identifying the

manufacturer and the device can be read from the

memory allowing programming equipment or ap-

plications to automatically match their interface to

the characteristics of the memory. The Electronic

Signature is output by giving the Read Electronic

Signature command. The manufacturer code is

output when all the Address inputs are at VIL. The

device code is output when A1 is at VIH and all the

a Read Memory Array command to return to Read

mode.

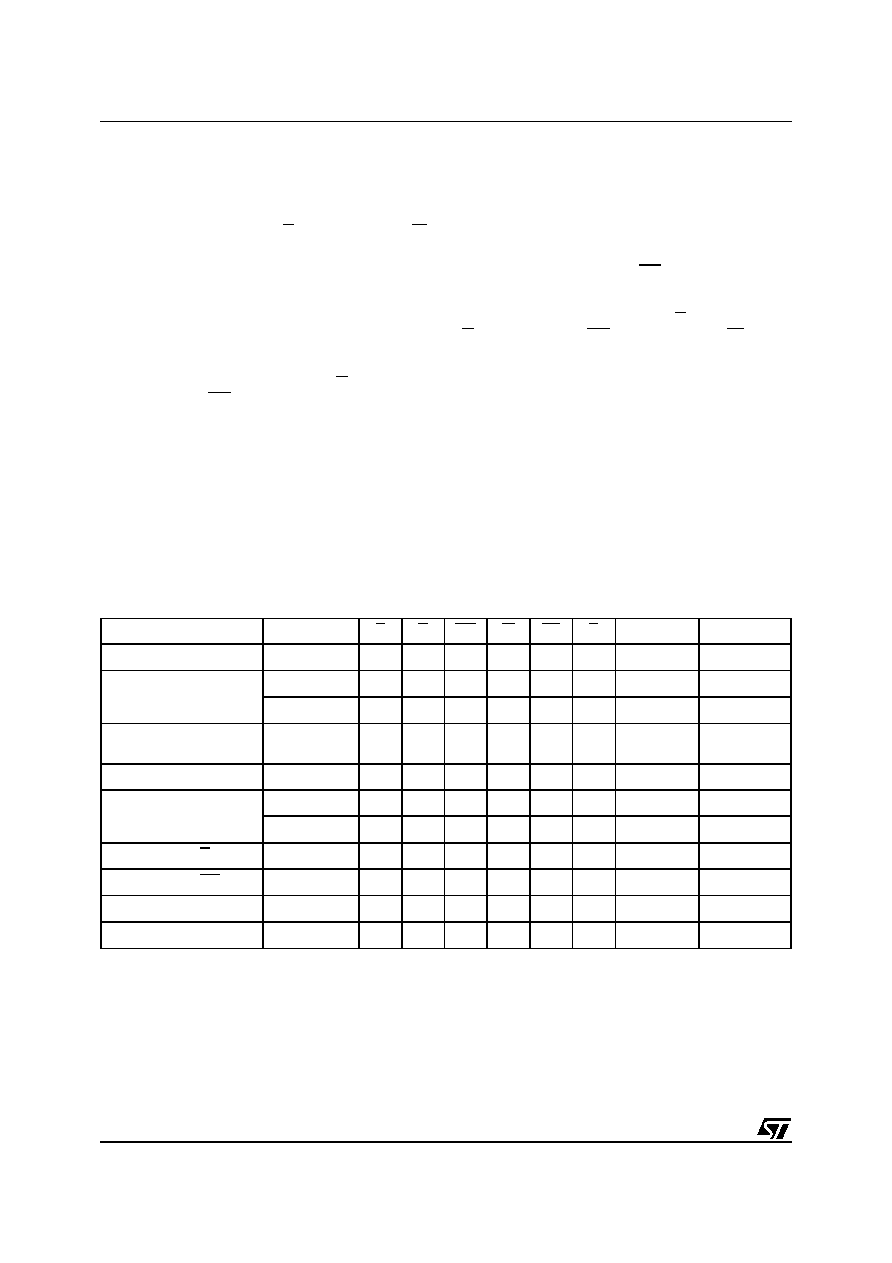

Table 4. Asynchronous Bus Operations

Note: X = Don’t Care

Bus Operation

Step

E

G

GD

W

RP

L

A0-A18

DQ0-DQ31

Asynchronous Bus Read

VIL

VIH

VIL

Address

Data Output

Asynchronous Latch

Controlled Bus Read

Address Latch

VIL

VIH

VIL

VIH

VIL

Address

High Z

Read

VIL

VIH

X

Data Output

Asynchronous Page

Read

VIL

VIH

X

Address

Data Output

Asynchronous Bus Write

VIL

VIH

X

VIL

VIH

VIL

Address

Data Input

Asynchronous Latch

Controlled Bus Write

Address Latch

VIL

VIH

VIL

Address

High Z

Write

VIL

VIH

X

VIL

VIH

X

Data Input

Output Disable, G

VIL

VIH

X

High Z

Output Disable, GD

VIL

VIH

X

High Z

Standby

VIH

XX

X

VIH

X

High Z

Reset/Power-Down

X

VIL

X

High Z

相關PDF資料 |

PDF描述 |

|---|---|

| M58BW016BT90ZA6 | 512K X 32 FLASH 3V PROM, 90 ns, PBGA80 |

| M58LR128FB95ZB6E | 8M X 16 FLASH 1.8V PROM, 95 ns, PBGA56 |

| M58LW128A150N1 | 8M X 16 FLASH 3V PROM, 150 ns, PDSO56 |

| M58WR064HU70ZB6U | 4M X 16 FLASH 1.8V PROM, 70 ns, PBGA44 |

| M59DR032F100N1T | 2M X 16 FLASH 1.8V PROM, 100 ns, PDSO48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M58BW016BB90ZA6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BBT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BBZA | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BT | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

| M58BW016BT100T3T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mbit 512Kb x32, Boot Block, Burst 3V Supply Flash Memories |

發(fā)布緊急采購,3分鐘左右您將得到回復。