- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370992 > M66272 (Mitsubishi Electric Corporation) LCD CONTROLLER with VRAM PDF資料下載

參數(shù)資料

| 型號: | M66272 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | LCD CONTROLLER with VRAM |

| 中文描述: | 液晶顯示控制器顯存 |

| 文件頁數(shù): | 3/4頁 |

| 文件大小: | 78K |

| 代理商: | M66272 |

LCD CONTROLLER with VRAM

M66272FP

MITSUBISHI <DIGITAL ASSP>

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

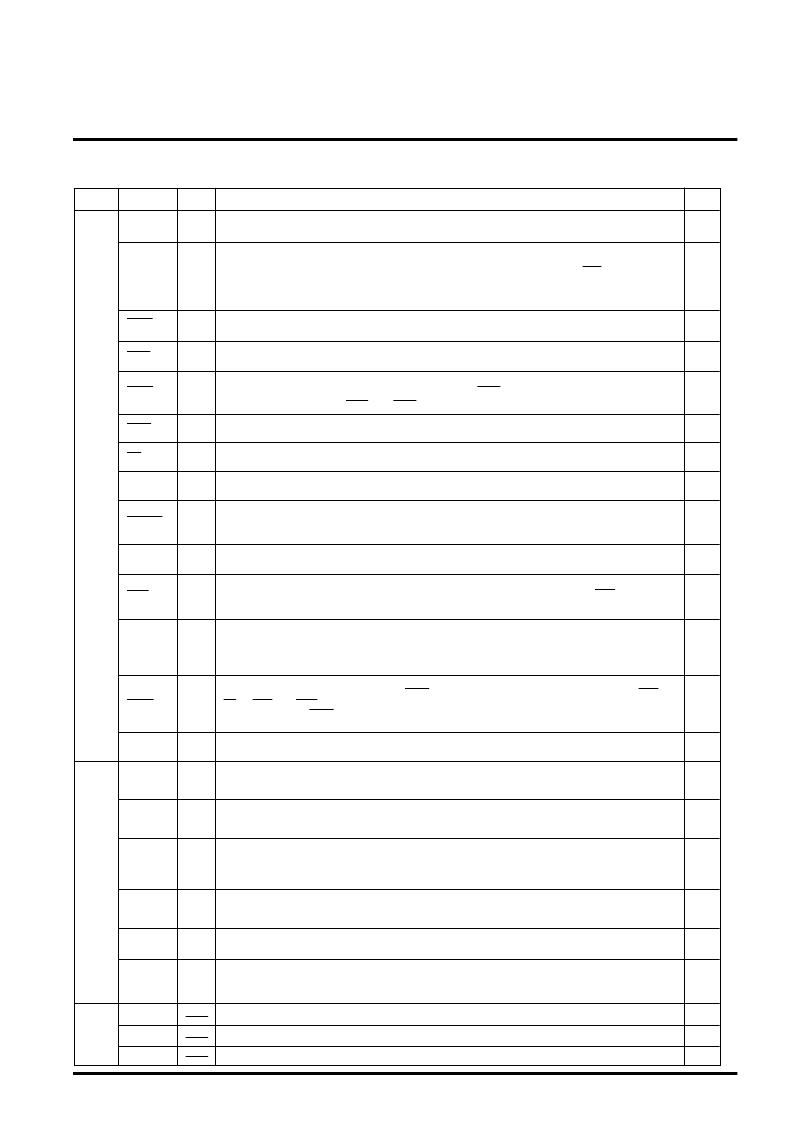

PIN DESCRIPTIONS

N.C

No connection

5

12

V

SS

Ground

7

V

DD

Power supply pin

Pin name

Input/

Output

Input/

Output

Function

Number

of pins

D<15:0>

MPU data bus

When selecting 8 bit MPU by MPUSEL input, connect D<15:8> to V

DD

or V

SS

.

16

1

HWR

A<14:0>

Input

15

MPU address bus

When selecting 8-bit MPU, use A<14:0>.

When selecting 16-bit MPU, use A<14:1> as a address bus. By combining A<0> and BHE, access to internal

VRAM can be gained.

When driving two screens (dual scan mode), notice that the allowable setup range of VRAM address is

restricted. Use A<7:0> for selecting address of control register.

Chip select input of control register

When this pin is "L", select the internal control register. Assign to I/O space of MPU.

Chip select input of VRAM

When this pin is "L", select the internal VRAM. Assign to memory space of MPU.

High-Write strobe input

When this pin is "L", write data to the internal VRAM. HWR is valid only in using 16-bit MPU

controlled byte access by LWR and HWR.

1

Low-Write strobe input

When this pin is "L", write data to the internal control register or VRAM.

Read strobe input

When this pin is "L", read data from the internal control register or VRAM.

8/16-bit MPU select input

According to MPU, set "V

SS

" for 8-bit MPU and set "V

DD

" for 16-bit MPU.

Reset input

Use reset signal of MPU. When this pin is "L", initialize (reset) all internal control registers and

counters.

MPU clock

Input system clock output from MPU.

Bus-High-Enable input

This pin is valid when using 16-bit MPU controlling byte access with A<0> and BHE.

Connect to "V

DD

" to select 8-bit MPU.

Bus swap input

When selecting 16-bit MPU, connect SWAP to “V

SS

” to transfer VD<n:0> in order of Upper/Lower byte of

MPU data bus, reversally connect to “V

DD

” in order of Lower/Upper byte.

When selecting 8-bit MPU, connect to “V

SS

”. Even if connecting to “V

DD

”, use D<7:0> to access to register of

8-bit width.

LWR

1

WAIT

WAIT output for MPU

This signal makes WAIT for MPU. Change WAIT to "L" at timing of falling edge of overlapping with MCS and

RD or LWR and HWR. And return to "H" at synchronization with the rising edge of MPUCLK after internal

processing. (Output WAIT only when requested access from MPU to VRAM is gained during cycle steal

access.)

Cycle Steal Enable output

State output of internal cycle steal access.

1

IOCS

1

MCS

1

RD

MPUSEL

1

1

RESET

MPUCLK

1

BHE

1

8

VD<7:0>

Display data bus for LCD

Transfer the LCD display data in synchronization with a rising edge of CP by putting 4-bit or 8-bit in parallel.

The VD<n:0> output pin in use differs depending on the number of driven screens and the display mode.

Display data transfer clock

Shift clock for the transfer of display data to LCD.

Take the display data of VD<n:0> to LCD at falling edge of CP.

Display data latch pulse

This clock use both as the latch pulse of display data for LCD and the transfer of scanning signal.

LP is output when it finishes transferring display data of a line.

Latch of display data and the transfer of scanning signal at falling edge of LP.

First Line Marker signal output

Output the start pulse of scanning line.

This signal is "H" active, the IC for driving scanning line catches FLM at falling edge of LP.

LCD alternating signal output

Signal for driving LCD by alternating current.

LCD (ON/OFF) control signal output

Output data which is set at bit "0" of mode register (R1) in the control register. This signal can be

used for controlling the LCD power supply, because LCDENB is set to "L" by RESET.

1

CP

1

LP

1

FLM

1

M

1

LCDENB

Item

MPU

interface

LCD

interface

Others

SWAP

1

3

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Output

Output

Output

Output

Output

Output

Output

CSE

1

Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66272FP | LCD CONTROLLER with VRAM |

| M66287FP | 262144-word x 8-bit x 3-FIELD MEMORY |

| M66307FP | LINE SCAN BUFFER with 16-BIT MPU BUS COMPATIBLE INPUTS |

| M66307SP | LINE SCAN BUFFER with 16-BIT MPU BUS COMPATIBLE INPUTS |

| M66312FP | 16-BIT LED DRIVER WITH SHIFT REGISTER AND LATCHED 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66272FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LCD CONTROLLER with VRAM |

| M66273FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LCD CONTROLLER with VRAM |

| M66280FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:5120 x 8-BIT LINE MEMORY |

| M66280FP(#TB0T) | 制造商:Renesas Electronics Corporation 功能描述: |

| M66281FP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:5120 × 8-Bit × 2 Line Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。