- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359091 > M7010R (意法半導(dǎo)體) 16K x 68-bit Entry NETWORK SEARCH ENGINE PDF資料下載

參數(shù)資料

| 型號: | M7010R |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 16K x 68-bit Entry NETWORK SEARCH ENGINE |

| 中文描述: | 16K的× 68位進入網(wǎng)絡(luò)搜索引擎 |

| 文件頁數(shù): | 34/67頁 |

| 文件大?。?/td> | 449K |

| 代理商: | M7010R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

M7010R

34/67

SEARCH COMMAND

The M7010R Search Engine can be configured in

three ways:

1. 68-bit

2. 136-bit

3. 272-bit

4. Mixed-sized SEARCHES on tables config-

ured with different widths

68-bit Configuration

Figure 25, page 35 shows the timing diagram for a

SEARCH operation in the 68-bit-configured table

(one device only). This illustration assumes that

the host ASIC has programmed TLSZ to '00,'

HLAT to '000,' LRAM to '1,' and LDEV to '1' in the

command register. The hardware diagram for this

search subsystem is shown in Figure 24.

–

Cycle A:

The host ASIC drives CMDV high and

applies the SEARCH command code (10) on

CMD[1:0]. CMD[5:3] must be driven by the in-

dex to the global mask register pair for use in

the SEARCH operation. CMD[8:6] signals must

be driven by the same bits that will be driven on

SADR[21:19] by this device if it has a hit.

DQ[67:0] must be driven with the data to be

compared. CMD[2] signal must be driven to log-

ic '0.'

–

Cycle B:

The host ASIC continues to drive

CMDV high and to apply the SEARCH com-

mand (10) on CMD[1:0]. CMD[5:2] must be driv-

en by the index of the comparand register pair

for storing the 136-bit word presented on the DQ

Bus during Cycles A and B. CMD[8:6] signals

must be driven with the index of the SSR that

will be used for storing the address of the

matching entry and the hit flag. The DQ[67:0]

continues to carry the 68-bit data to be com-

pared.

Note:

In the 68-bit configuration, the host ASIC

must supply the same data on DQ[67:0] during

cycles A and B. The even and odd GMR pairs

selected for the compare must be programmed

with the same value.

The SEARCH command is a pipelined operation

and executes a SEARCH at half their rate of fre-

quency of CLK2X for 68-bit searches in x68-con-

figured tables. The latency of SADR, CE_L,

ALE_L, WE_L,

SSV,

SEARCH Command cycle (= two CLK2X cycles)

is shown in Table 27, page 36.

The timing diagram for all SRAM interface signals,

SSV, and SSF shift to the right for different values

of TLSZ, as specified in Table 25, page 36 and Ta-

ble 26, page 36.

In addition, SSV and SSF shift to the right for dif-

ferent values of HLAT, as specified in Table 26,

page 36.

68-bit Configuration with LDEV = 1.

The

vice is configured to be the last in the depth-cas-

caded table by setting LDEV to '1' in the Command

Register. The device with LDEV set to '1' drives

the SSF and SSV signals in cycles when all up-

stream devices do not drive these signals. The

M7010R with its LDEV Bit set drives SSF and SSV

during a search with a miss or with non-search

commands (see the LDEV Bit definition in Table

10, page 20).

68-bit Configuration with LRAM = 1.

Setting

LRAM to '1' in the Command Register configures

the device to be the last on the SRAM Bus. In a cy-

cle where the upstream device does not drive the

SRAM Bus, the last device of the SRAM Bus (with

LRAM = 1) drives the bus (SADR, CE_L, WE_L,

ALE_L) when they are active. When set to '1,' the

LRAM Bit sets the default driver for the SRAM con-

trol signals (SADR, CE_L, WE_L, and ALE_L).

and

SSF

from

68-bit

de-

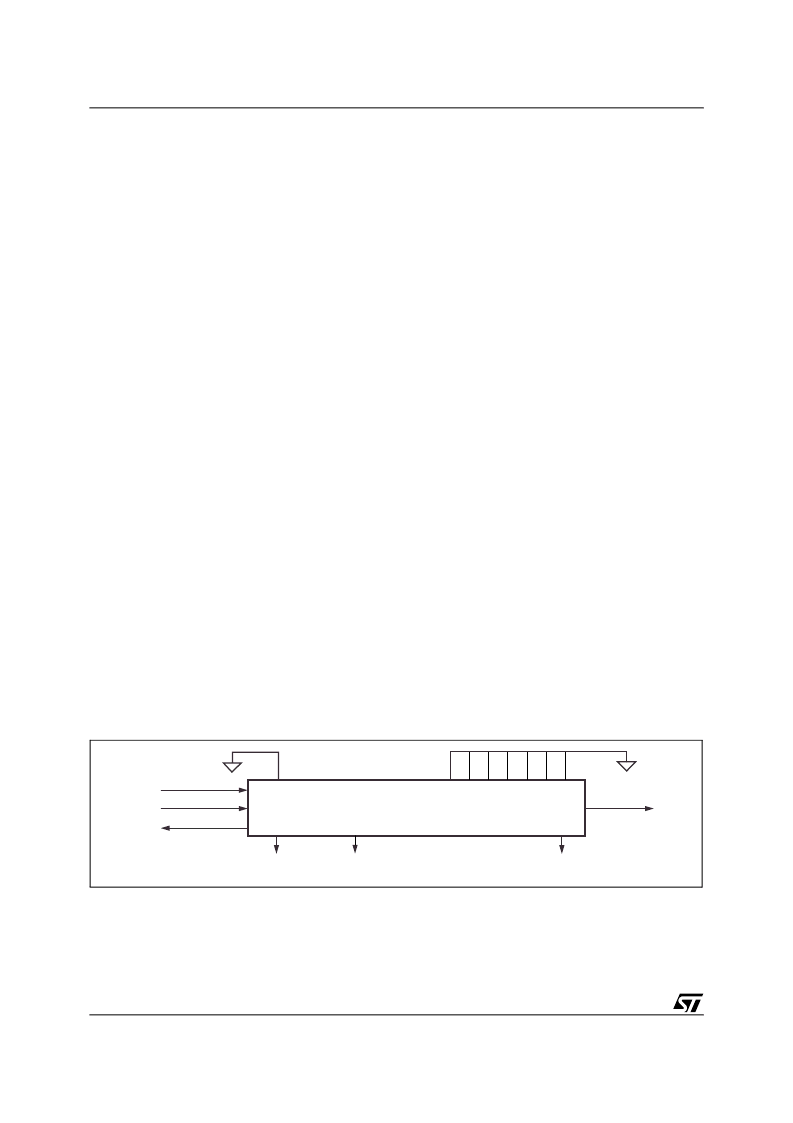

Figure 24. Hardware Diagram for a Table with a Single Device (68-bit Operation)

DQ[67:0]

CMDV, CMD[8:0]

SSF, SSV

SRAM

LHO[1]

BHI[2:0]

BHI[2:0]

LHI

3

2

1

0

M7010R

LHO[0]

6

5

4

AI07040

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M7020R-050ZA1T | CAP TANT 22UF 10V 20% POLY SMD |

| M7020R-066ZA1T | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M7020R-083ZA1T | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M7020R | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M72DW64000B | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M7010R-066ZA1T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16K x 68-bit Entry NETWORK SEARCH ENGINE |

| M7010R-083ZA1T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16K x 68-bit Entry NETWORK SEARCH ENGINE |

| M701-220442 | 功能描述:USB接頭 USB A SINGLE PC TAIL HORIZONTAL RoHS:否 制造商:FCI 產(chǎn)品:USB Type A Connectors 標(biāo)準(zhǔn):USB 3.0 端口數(shù)量: 位置/觸點數(shù)量:9 型式:Female 電流額定值:1.8 A 安裝風(fēng)格:Through Hole 端接類型:Solder Pin 連接器類型:USB 3.0 Receptacle |

| M7012250442 | 制造商:Harwin 功能描述: |

| M701-2250442R | 制造商:Harwin 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。