- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11564 > MAX3421EEHJ+T (Maxim Integrated Products)IC USB PERIPH/HOST CNTRL 32TQFP PDF資料下載

參數(shù)資料

| 型號: | MAX3421EEHJ+T |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 26/28頁 |

| 文件大小: | 0K |

| 描述: | IC USB PERIPH/HOST CNTRL 32TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 2,500 |

| 控制器類型: | USB 外設(shè)控制器 |

| 接口: | USB/串行 |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 15mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-TQFP |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(5x5) |

| 包裝: | 帶卷 (TR) |

| 配用: | MAX3421EVKIT-1+-ND - EVAL KIT FOR MAX3421E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁

MAX3421E

USB Peripheral/Host Controller

with SPI Interface

7

Maxim Integrated

Register Description

The SPI master controls the MAX3421E by reading and

writing 26 registers in peripheral mode (see Table 1) or

reading and writing 23 registers in host mode (see Table

2). Setting the HOST bit in the MODE (R27) register con-

figures the MAX3421E for host operation. When operating

as a USB peripheral, the MAX3421E is register-compati-

ble with the MAX3420E with the additional features listed

in Note 1b below Table 1. For a complete description of

register contents, refer to the

MAX3421E Programming

Guide on the Maxim website.

A register access consists of the SPI master first writing

an SPI command byte followed by reading or writing the

contents of the addressed register. All SPI transfers are

MSB first. The command byte contains the register

address, a direction bit (read = 0, write = 1), and the

ACKSTAT bit (Figure 5). The SPI master addresses the

MAX3421E registers by writing the binary value of the

register number in the Reg4 through Reg0 bits of the

command byte. For example, to access the IOPINS1

(R20) register, the Reg4 through Reg0 bits would be as

follows: Reg4 = 1, Reg3 = 0, Reg2 = 1, Reg1 = 0, Reg0

= 0. The DIR (direction) bit determines the direction for

the data transfer. DIR = 1 means the data byte(s) are

written to the register, and DIR = 0 means the data

byte(s) are read from the register. The ACKSTAT bit sets

the ACKSTAT bit in the EPSTALLS (R9) register (periph-

eral mode only). The SPI master sets this bit to indicate

that it has finished servicing a CONTROL transfer. Since

the bit is frequently used, having it in the SPI command

byte improves firmware efficiency. The ACKSTAT bit is

ignored in host mode. In SPI full-duplex mode, the

MAX3421E clocks out eight USB status bits as the com-

mand byte is clocked in (Figures 6, 7). In half-duplex

mode, these status bits are accessed as register bits.

The first five registers (R0–R4) address FIFOs in both

peripheral and host modes. Repeated accesses to these

registers freeze the internal register address so that mul-

tiple bytes may be written to or read from a FIFO in the

same SPI access cycle (while

SS is low). Accesses to

registers R5–R19 increment the internal register address

for every byte transferred during the SPI access cycle.

Accessing R20 freezes access at that register, access-

ing R21–R31 increments the internal address, and

repeated accesses to R31 freeze at R31.

The register maps in Table 1 and Table 2 show which

register bits apply in peripheral and host modes.

Register bits that do not apply to a particular mode are

shown as zeros. These register bits read as zero values

and should not be written to with a logic 1.

Register Map in Peripheral Mode

The MAX3421E maintains register compatibility with the

MAX3420E when operating in USB peripheral mode

(MAX3421E HOST bit is set to 0 (default)). Firmware

written for the MAX3420E runs without modification on

the MAX3421E. To support new MAX3421E features,

the register set includes new bits, described in Note 1b

at the bottom of Table 1.

Register Map in Host Mode

As Table 2 shows, in host mode (HOST = 1), some

MAX3420E registers are renamed (for example R1

becomes RCVFIFO), some are not used (shown with

zeros), and some still apply to host mode. In addition, 11

registers (R21–R31) add the USB host capability.

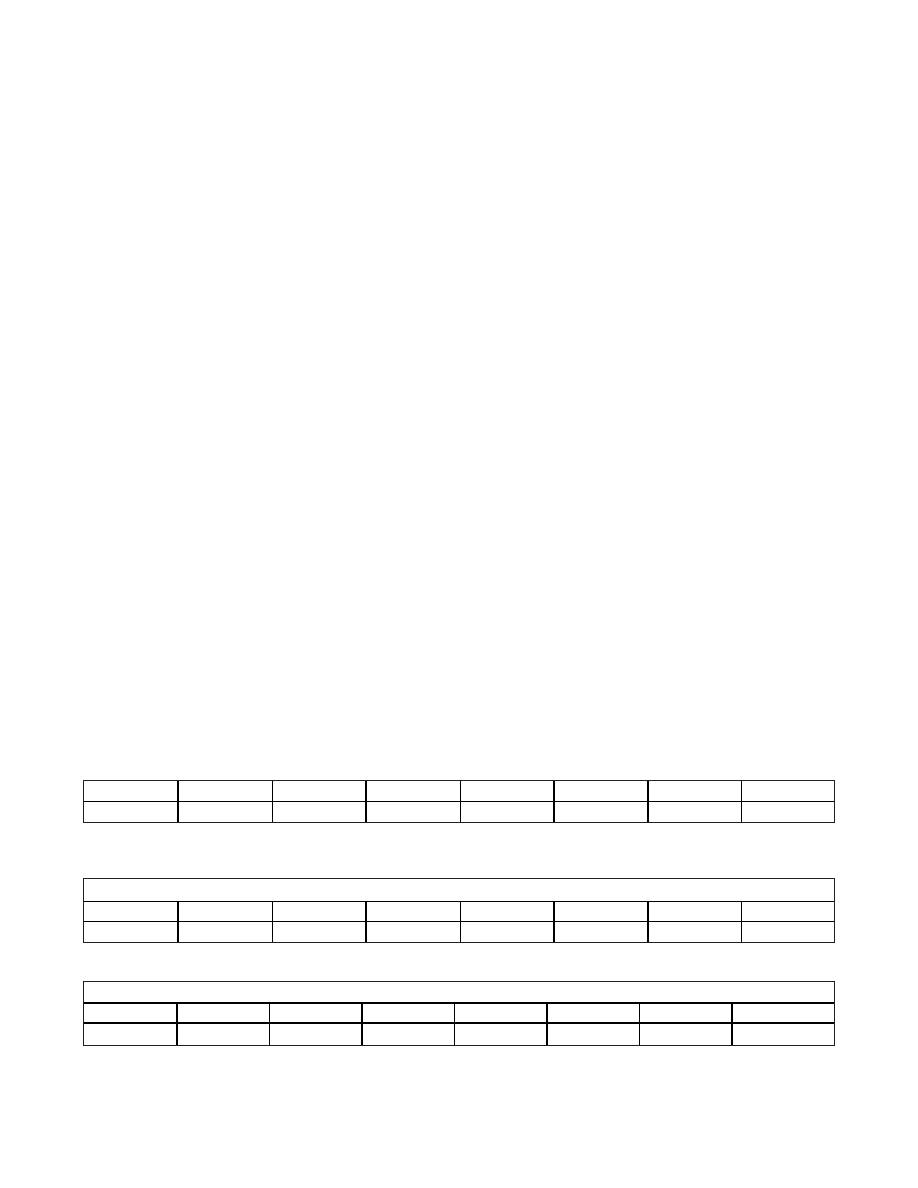

Figure 7. USB Status Bits Clocked Out as First Byte of Every Transfer in Host Mode (Full-Duplex Mode Only)

STATUS BITS (HOST MODE)

b7

b6

b5

b4

b3

b2

b1

b0

HXFRDNIRQ

FRAMEIRQ

CONNIRQ

SUSDNIRQ

SNDBAVIRQ

RCVDAVIRQ

RSMREQIRQ

BUSEVENTIRQ

*

The ACKSTAT bit is ignored in host mode.

Figure 5. SPI Command Byte

b7

b6

b5

b4

b3

b2

b1

b0

Reg4

Reg3

Reg2

Reg1

Reg0

0

DIR

ACKSTAT*

Figure 6. USB Status Bits Clocked Out as First Byte of Every Transfer in Peripheral Mode (Full-Duplex Mode Only)

STATUS BITS (PERIPHERAL MODE)

b7

b6

b5

b4

b3

b2

b1

b0

SUSPIRQ

URESIRQ

SUDAVIRQ

IN3BAVIRQ

IN2BAVIRQ

OUT1DAVIRQ

OUT0DAVIRQ

IN0BAVIRQ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GRM2165C1H510JZ01J | CAP CER 51PF 50V 5% NP0 0805 |

| MAX3421EETJ+T | IC USB PERIPH/HOST CNTRL 32TQFN |

| V375C28M75B3 | CONVERTER MOD DC/DC 28V 75W |

| MAX5942BESE+ | IC IEEE 802.3AF POE SYSTM 16SOIC |

| 78Q8430-100IGTR/F | IC LAN MEDIA ACCESS CTLR 100LQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3421EETJ+ | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3421EETJ+T | 功能描述:外圍驅(qū)動器與原件 - PCI USB Peripheral Controller w/SPI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| MAX3421EVKIT-1+ | 功能描述:界面開發(fā)工具 MAX3421E/20E Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| MAX3430CPA | 功能描述:RS-485接口IC RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| MAX3430CPA+ | 功能描述:RS-485接口IC Fail-Safe 1/4-Unit 3.3V Transceiver RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。