- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9673 > MAX3676EHJ+ (Maxim Integrated Products)IC CLOCK RECOVERY 32-TQFP PDF資料下載

參數(shù)資料

| 型號: | MAX3676EHJ+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 4/15頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CLOCK RECOVERY 32-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 360 |

| 類型: | 時鐘和數(shù)據(jù)恢復(fù)(CDR),多路復(fù)用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 輸入: | PECL |

| 輸出: | PECL |

| 電路數(shù): | 1 |

| 比率 - 輸入:輸出: | 2:2 |

| 差分 - 輸入:輸出: | 是/是 |

| 頻率 - 最大: | 622.08MHz |

| 電源電壓: | 3 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-TQFP |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(5x5) |

| 包裝: | 托盤 |

MAX3676

622Mbps, 3.3V Clock-Recovery and

Data-Retiming IC with Limiting Amplifier

12

______________________________________________________________________________________

Optical receivers, incorporating transimpedance

preamplifiers and limiting postamplifiers, can signifi-

cantly clean up the effects of dispersion and attenua-

tion. In addition, these amplifiers can provide fast

transitions with minimal aberrations to the subsequent

CDR blocks. However, these stages also add distor-

tions to the midpoint crossing, contributing to timing jit-

ter. Timing jitter is one of the most critical technical

issues to consider when developing optical receivers

and CDR circuits.

A better understanding of the different sources of jitter

helps in the design and application of optical receiver

modules and integrated CDR solutions. SDH/SONET

specifications are well defined regarding the amount of

jitter tolerance allowed at the inputs of optical receivers,

as well as jitter peaking requirements, but they do little

to define the different sources of jitter. The jitter that

must be tolerated at an optical receiver input involves

three significant sources, all of which are present in

varying degrees in typical receiver systems:

1) Random jitter (RJ)

2) Pattern-dependent jitter (PDJ)

3) Pulse-width distortion (PWD)

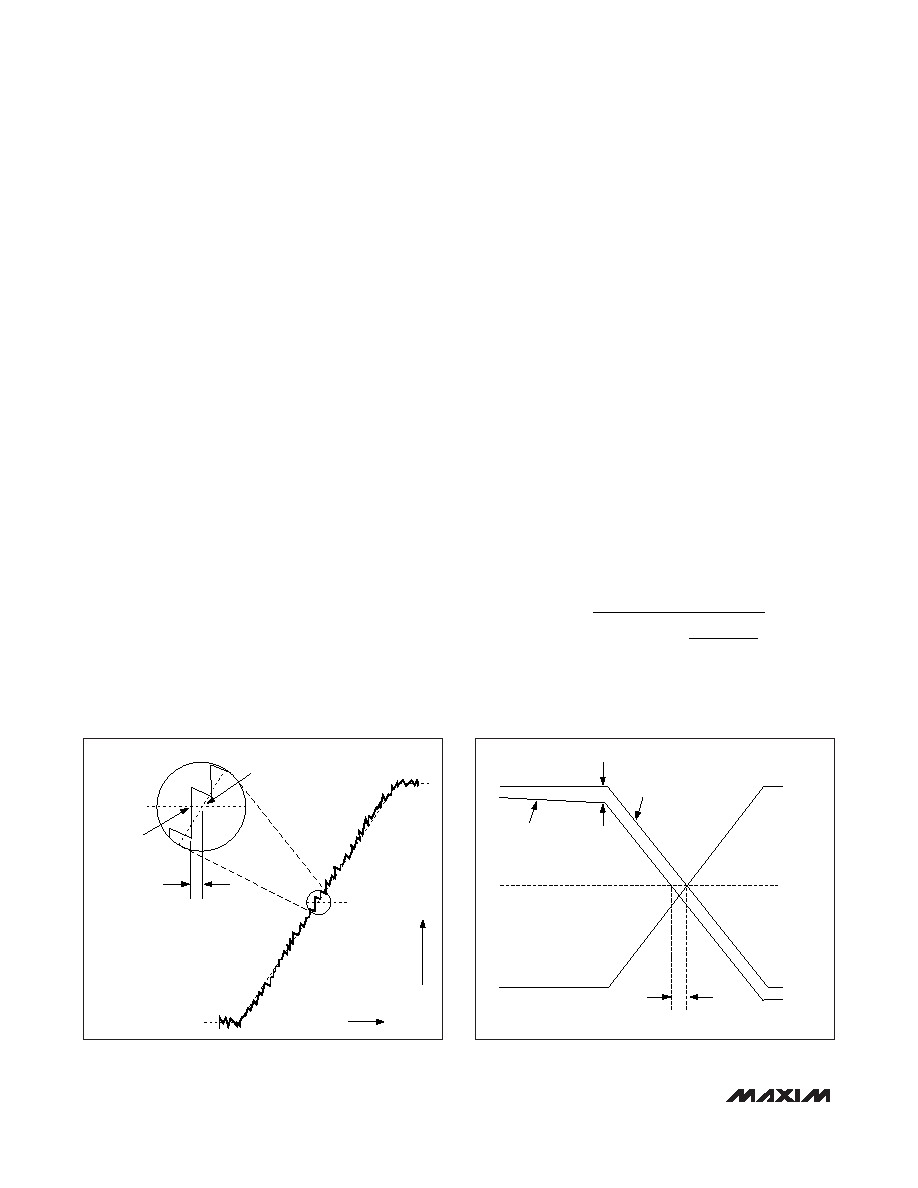

Random Jitter

RJ is caused by random noise present during edge

transitions (Figure 8). This random noise results in ran-

dom midpoint crossings. All electrical systems gener-

ate some random noise; however, the faster the speed

of the transitions, the lower the effect of noise on ran-

dom jitter. The following equation is a simple worst-

case estimation of random jitter:

RJ (rms) = (rms noise)/(slew rate)

Pattern-Dependent Jitter

PDJ results from wide variations in the number of con-

secutive bits contained in NRZ data streams working

against the bandwidth requirements of the receiver

(Figure 9). The location of the lower -3dB cutoff fre-

quency is important, and must be set to pass the low

frequencies associated with long consecutive bit

streams. AC-coupling is common in optical receiver

design.

When using a preamplifier with a highpass frequency

response, select the input AC-coupling capacitor, CIN,

to provide a low-frequency cutoff (fC) one decade lower

than the preamplifier low-frequency cutoff. As a result,

the PDJ is dominated by the low-frequency cutoff of

the preamplifier.

When using a preamplifier without a highpass response

with the MAX3676, the following equation provides a

good starting point for choosing CIN:

where tL = duration of the longest run of consecutive

bits of the same value (seconds); PDJ = maximum

C

-t

1.25k

In

PDJ BW

IN

L

≥

() ()( )

Ω

.

1

05

MIDPOINT

RANDOM

JITTER

ACTUAL

MIDPOINT

CROSSING

DESIRED

MIDPOINT

CROSSING

0–1

TRANSITION

WITH RANDOM

NOISE

TIME

AMPLITUDE

Figure 8. Random Jitter on Edge Transition

AMPLITUDE

TIME

MIDPOINT

LONG

CONSECUTIVE

BIT STREAM

0-1-0 BIT STREAM

LF DROOP

LF PDJ

Figure 9. Pattern-Dependent Jitter Due to Low-Frequency

Cutoff

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADN2813ACPZ | IC CLK/DATA REC 1.25GBPS 48LFCSP |

| AD800-52BRZ | IC CLK\DATA RECOVERY PLL 20SOIC |

| SY87700VZH | IC CLK/DATA RECOVERY 3.3V 28SOIC |

| MS27467P25B35PC | CONN PLUG 128POS STRAIGHT W/PINS |

| AD9558BCPZ | IC CLOCK TRANSLATOR 64LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3676EHJ+ | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 622Mbps 3.3V Clock Recovery RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MAX3676EHJ+T | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 622Mbps 3.3V Clock Recovery RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MAX3676EHJ-T | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 622Mbps 3.3V Clock Recovery RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MAX3677CTJ+ | 制造商:Microsemi Corporation 功能描述:+3.3V, LOW-JITTER CLOCK GEN W/MULT OUT - Trays 制造商:Microsemi Corporation 功能描述:Microsemi MAX3677CTJ+ Clocks - Timers 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CLOCK GENERATOR PROGR 32TQFN 制造商:Microsemi Corporation 功能描述:IC CLOCK GENERATOR PROGR 32TQFN |

| MAX3677CTJ+T | 制造商:Microsemi Corporation 功能描述:+3.3V, LOW-JITTER CLOCK GEN W/MULT OUT - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。