- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄5814 > MAX3798ETJ+ (Maxim Integrated Products)IC LIMITING AMP/VCSEL DVR 32TQFN PDF資料下載

參數(shù)資料

| 型號: | MAX3798ETJ+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 8/35頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC LIMITING AMP/VCSEL DVR 32TQFN |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 放大器類型: | 限制 |

| 電路數(shù): | 1 |

| 輸出類型: | 差分 |

| 電流 - 電源: | 97mA |

| 電壓 - 電源,單路/雙路(±): | 2.85 V ~ 3.63 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 32-TQFN-EP(5x5) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 1387 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

MAX3798

1.0625Gbps to 10.32Gbps, Integrated, Low-

Power SFP+ Limiting Amplifier and VCSEL Driver

16

______________________________________________________________________________________

Dual Path Limiter

The limiting amplifier features a high-gain mode and a

high-bandwidth mode allowing for overall system opti-

mization. Either the MSEL pin or the MODE_SEL bit can

perform the mode selection. For operating up to

4.25Gbps, the high-gain mode (MODE_SEL = 0) is rec-

ommended. For operating above 8.5Gbps, the high-

bandwidth mode (MODE_SEL = 1) is recommended.

For operations at 8.5Gbps, the mode selection is

dependent on the performance of the receiver optical

subassembly. The polarity of ROUT+/ROUT- relative to

RIN+/RIN- is programmed by the RX_POL bit.

Offset Correction Circuitry

The offset correction circuit is enabled to remove pulse-

width distortion caused by intrinsic offset voltages with-

in the differential amplifier stages. An external capacitor

(CAZ) connected between the CAZ1 and CAZ2 pins is

used to set the offset correction loop cutoff frequency.

The offset loop can be disabled using the AZ_EN bit.

The MAX3798 contains a feature that allows the part to

meet a 10μs mode-select switching time. The mode-

select switching time can be adjusted using the GMEN

and CAZX bits.

CML Output Stage with Deemphasis and

Slew-Rate Control

The CML output stage is optimized for differential 100

Ω

loads. The RXDE_EN bit adds analog deemphasis

compensation to the limited differential output signal for

SFP connector losses. The output stage is controlled by

a combination of the RX_EN and SQ_EN bits and the

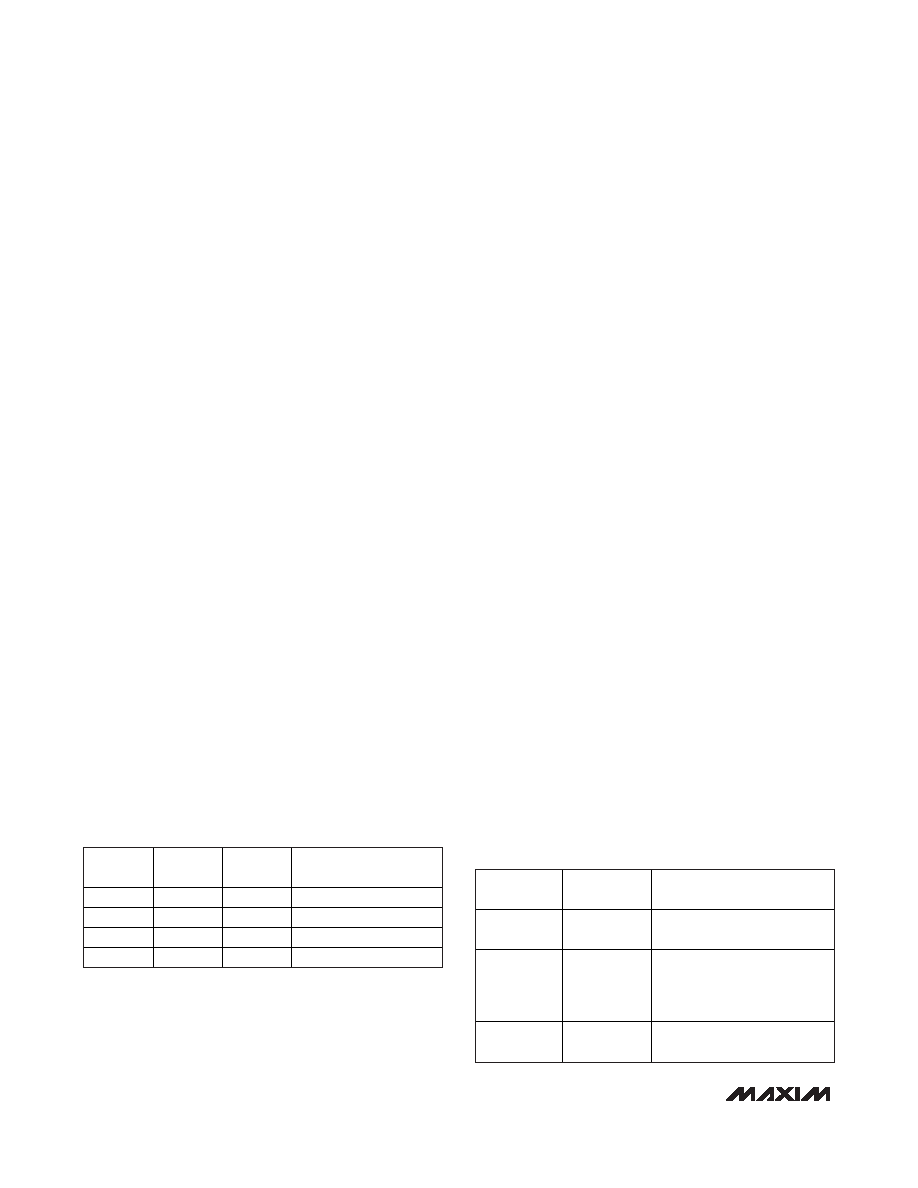

LOS pin. See Table 1.

Amplitude of the CML output stage is controlled by an

8-bit DAC register (SET_CML). The differential output

amplitude range is from 40mVP-P up to 1200mVP-P with

4.6mVP-P resolution (assuming an ideal 100

Ω differen-

tial load).

The lower bandwidth data path allows for reduction of

output edge speed in order to enhance EMI perfor-

mance. The SLEW_RATE bit controls the slew rate of

the output stage (see Table 2).

Loss-of-Signal (LOS) Circuitry

The input data amplitude is compared to a preset

threshold controlled by the 6-bit DAC register

SET_LOS. The LOS assert level can be programmed

from 14mVP-P up to 77mVP-P with 1.5mVP-P resolution

(assuming an ideal 100

Ω differential source). LOS is

enabled through the LOS_EN bit and the polarity of the

LOS is controlled with the LOS_POL bit.

VCSEL Driver

The VCSEL driver inside the MAX3798 is designed to

operate from 1.0625Gbps to 10.32Gbps. The transmit-

ter contains a differential data path with pulse-width

adjustment, bias current and modulation current DACs,

output driver with programmable deemphasis, power-

on reset circuitry, BIAS monitor, VCSEL current limiter,

and eye safety circuitry. A 3-wire digital interface is

used to control the transmitter functions. The registers

that control the transmitter functionality are TXCTRL,

TXSTAT1, TXSTAT2, SET_IBIAS, SET_IMOD, IMOD-

MAX, IBIASMAX, MODINC, BIASINC, MODECTRL,

SET_PWCTRL, and SET_TXDE.

Differential Data Path

The CML input buffer is optimized for AC-coupled sig-

nals and is internally terminated with a differential 100

Ω.

Differential input data is equalized for high-frequency

losses due to SFP connectors. The TX_POL bit in the

TXCTRL register controls the polarity of TOUT+ and

TOUT- vs. TIN+ and TIN-. The SET_PWCTRL register

RX_EN

SQ_EN

LOS

OPERATION MODE

DESCRIPTION

0

X

CML output disabled.

1

0

X

CML output enabled.

1

0

CML output enabled.

1

CML output disabled.

Table 1. CML Output Stage Operation Mode

MODE_SEL

SLEW_RATE

OPERATION MODE

DESCRIPTION

0

4.25Gbps operation with

reduced output edge speed.

0

1

4.25Gbps operation with full

edge speed; 8.5Gbps

operation with high bandwidth

ROSA.

1

X

8.5Gbps with lower bandwidth

ROSA; 10.32Gbps operation.

Table 2. Slew-Rate Control for CML

Output Stage

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BK1/S506-6.3-R | FUSE 6.3A 250V TLAG GLS 5X20 IEC |

| BK/S506-5-R | FUSE 5A 250V T-LAG GLASS S506 |

| 2095-300-BLF | SURGE ARRESTOR GDT 3000V AXIAL |

| BK/ATC-1 | FUSE BLADE 1A 32V BLACK UL |

| 2095-200-BLF | SURGE ARRESTOR GDT 2000V AXIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3798ETJ+ | 功能描述:激光驅(qū)動器 1.0625-10.32Gbps SFP w/VCSEL Driver RoHS:否 制造商:Micrel 數(shù)據(jù)速率:4.25 Gbps 工作電源電壓:3 V to 3.6 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-16 封裝:Tube |

| MAX3798ETJ+T | 功能描述:激光驅(qū)動器 1.0625-10.32Gbps SFP w/VCSEL Driver RoHS:否 制造商:Micrel 數(shù)據(jù)速率:4.25 Gbps 工作電源電壓:3 V to 3.6 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-16 封裝:Tube |

| MAX3799E/D | 功能描述:限幅放大器 1Gbps to 14Gbps SFP+ Multirate Limiting Amplifier and VCSEL Driver RoHS:否 制造商:Micrel 輸入電壓范圍(最大值):3.6 V 工作電源電壓:3.3 V 電源電流:40 mA 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:MSOP-10 封裝:Tube |

| MAX3799ETJ+ | 功能描述:限幅放大器 1-14Gbps SFP w/VCSEL Driver RoHS:否 制造商:Micrel 輸入電壓范圍(最大值):3.6 V 工作電源電壓:3.3 V 電源電流:40 mA 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:MSOP-10 封裝:Tube |

| MAX3799ETJ+T | 功能描述:限幅放大器 1-14Gbps SFP w/VCSEL Driver RoHS:否 制造商:Micrel 輸入電壓范圍(最大值):3.6 V 工作電源電壓:3.3 V 電源電流:40 mA 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:MSOP-10 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。