- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383540 > MAX9222ETM (MAXIM INTEGRATED PRODUCTS INC) Programmable DC-Balance 21-Bit Deserializers PDF資料下載

參數(shù)資料

| 型號: | MAX9222ETM |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | Programmable DC-Balance 21-Bit Deserializers |

| 中文描述: | QUAD LINE RECEIVER, PQCC48 |

| 封裝: | 7 X 7 MM, 0.80 MM HEIGHT, MO-220, TQFN-48 |

| 文件頁數(shù): | 11/18頁 |

| 文件大小: | 904K |

| 代理商: | MAX9222ETM |

M

Programmable DC-Balance

21-Bit Deserializers

______________________________________________________________________________________

11

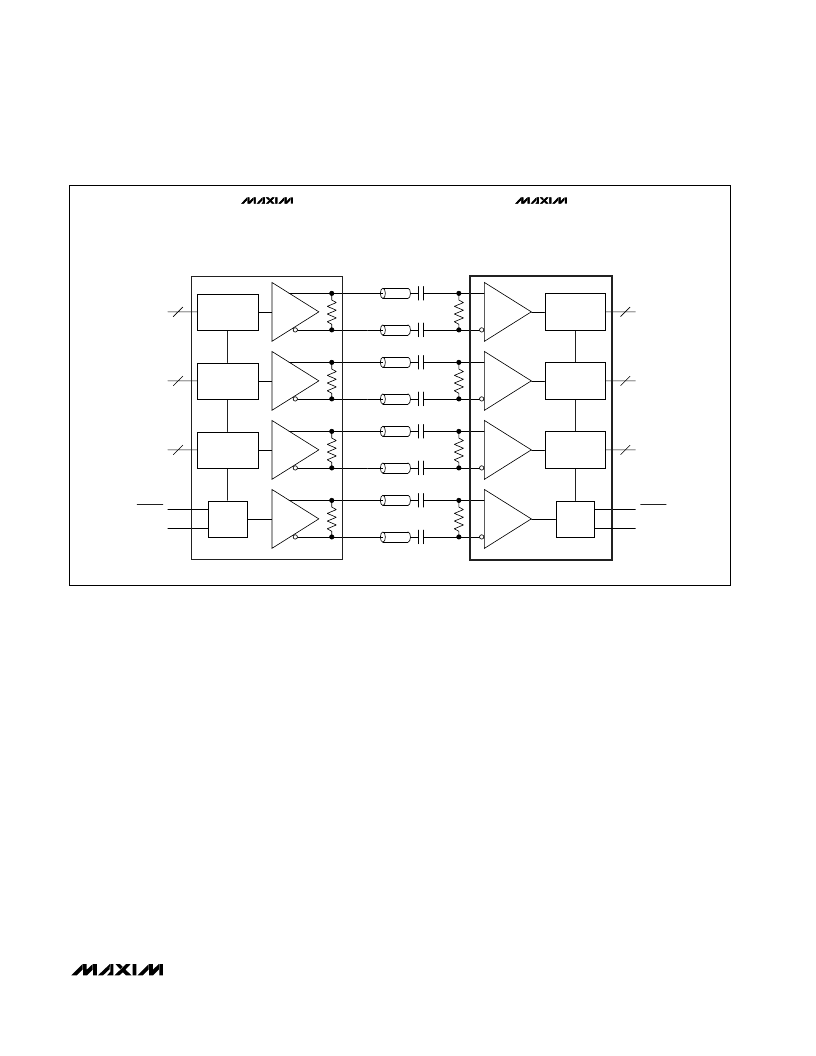

The RC network for an AC-coupled link consists of the

LVDS receiver termination resistor (R

T

), the LVDS driver

output resistor (R

O

), and the series AC-coupling capac-

itors (C). The RC time constant for two equal-value

series capacitors is (C x (R

T

+ R

O

))/2 (Figure 12). The

RC time constant for four equal-value series capacitors

is (C x (R

T

+ R

O

))/4 (Figure 13).

R

T

is required to match the transmission line imped-

ance (usually 100

) and R

O

is determined by the LVDS

driver design (the minimum differential output resis-

tance of 78

for the MAX9209/MAX9211/MAX9213/

MAX9215 serializers is used in the following example).

This leaves the capacitor selection to change the sys-

tem time constant.

In the following example, the capacitor value for a

droop of 2% is calculated. Jitter due to this droop is

then calculated assuming a 1ns transition time:

C = - (2 x t

B

x DSV) / (ln (1 - D) x (R

T

+ R

O

)) (Eq 1)

where:

C = AC-coupling capacitor (F).

t

B

= bit time (s).

DSV = digital sum variation (integer).

ln = natural log.

D = droop (% of signal amplitude).

R

T

= termination resistor (

).

R

O

= output resistance (

).

Equation 1 is for two series capacitors (Figure 12). The

bit time (t

B

) is the period of the parallel clock divided by

9. The DSV is 10. See equation 3 for four series capaci-

tors (Figure 13).

The capacitor for 2% maximum droop at 8MHz parallel

rate clock is:

C = - (2 x t

B

x DSV) / (ln (1 - D) x (R

T

+ R

O

))

C = - (2 x 13.9ns x 10) / (ln (1 - 0.02) x (100

+ 78

))

C = 0.0773μF

(7 + 2):1

1:(9 - 2)

7

7

100

(7 + 2):1

1:(9 - 2)

7

7

100

(7 + 2):1

1:(9 - 2)

7

7

100

PLL

PLL

100

MAX9209

MAX9211

MAX9213

MAX9215

MAX9210

MAX9212

MAX9214

MAX9216

MAX9220

MAX9222

TxOUT

TxCLK OUT

RxIN

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT

PWRDWN

TxCLK IN

TxIN

HIGH-FREQUENCY, CERAMIC

SURFACE-MOUNT CAPACITORS

CAN ALSO BE PLACED AT THE

SERIALIZER INSTEAD OF THE DESERIALIZER.

Figure 12. Two Capacitors per Link, AC-Coupled, DC-Balanced Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9216ETM | Programmable DC-Balance 21-Bit Deserializers |

| MAX922CUA | Ultra Low-Power, Single/Dual-Supply Comparators |

| MAX921-MAX924 | Ultra Low-Power, Single/Dual-Supply Comparators |

| MAX922 | Ultra Low-Power, Single/Dual-Supply Comparators |

| MAX923 | Ultra Low-Power, Single/Dual-Supply Comparators |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9222EUM | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Programmable DC-Balance 21-Bit Deserializers |

| MAX9222EUM+ | 制造商:Maxim Integrated Products 功能描述:LVDS DESERLIZER 48TSSOP - Rail/Tube |

| MAX9222EUM+D | 制造商:Maxim Integrated Products 功能描述:LVDS DESERLIZER 48TSSOP - Rail/Tube |

| MAX9222EUM+T | 制造商:Maxim Integrated Products 功能描述:LVDS DESERLIZER 48TSSOP - Tape and Reel |

| MAX9222EUM+TD | 制造商:Maxim Integrated Products 功能描述:- Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。