- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371076 > MC908QL2V (Motorola, Inc.) Microcontrollers PDF資料下載

參數(shù)資料

| 型號: | MC908QL2V |

| 廠商: | Motorola, Inc. |

| 英文描述: | Microcontrollers |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 53/222頁 |

| 文件大小: | 2861K |

| 代理商: | MC908QL2V |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當(dāng)前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁

Registers

MC68HC908QL4 MC68HC908QL3 MC68HC908QL2 Data Sheet, Rev. 4

Freescale Semiconductor

53

(with ACLKEN low), continuous conversions will cease and can be restarted only with a write to

ADCSC. Any write to ADCSC with ADCO set and the ADCH bits not all 1s will abort the current

conversion and begin continuous conversions.

If the bus frequency is less than the ADCK frequency, precise sample time for continuous conversions

cannot be guaranteed in short-sample mode (ADLSMP = 0). If the bus frequency is less than 1/11th

of the ADCK frequency, precise sample time for continuous conversions cannot be guaranteed in

long-sample mode (ADLSMP = 1).

When clear, the ADC10 will perform a single conversion (single conversion mode) each time ADCSC

is written (assuming the ADCH[4:0] bits do not decode all 1s).

1 = Continuous conversion following a write to ADCSC

0 = One conversion following a write to ADCSC

ADCH[4:0] —

Channel Select Bits

The ADCH[4:0] bits form a 5-bit field that is used to select one of the input channels. The input

channels are detailed in

Table 3-2

. The successive approximation converter subsystem is turned off

when the channel select bits are all set to 1. This feature allows explicit disabling of the ADC10 and

isolation of the input channel from the I/O pad. Terminating continuous conversion mode this way will

prevent an additional, single conversion from being performed. It is not necessary to set the channel

select bits to all 1s to place the ADC10 in a low-power state, however, because the module is

automatically placed in a low-power state when a conversion completes.

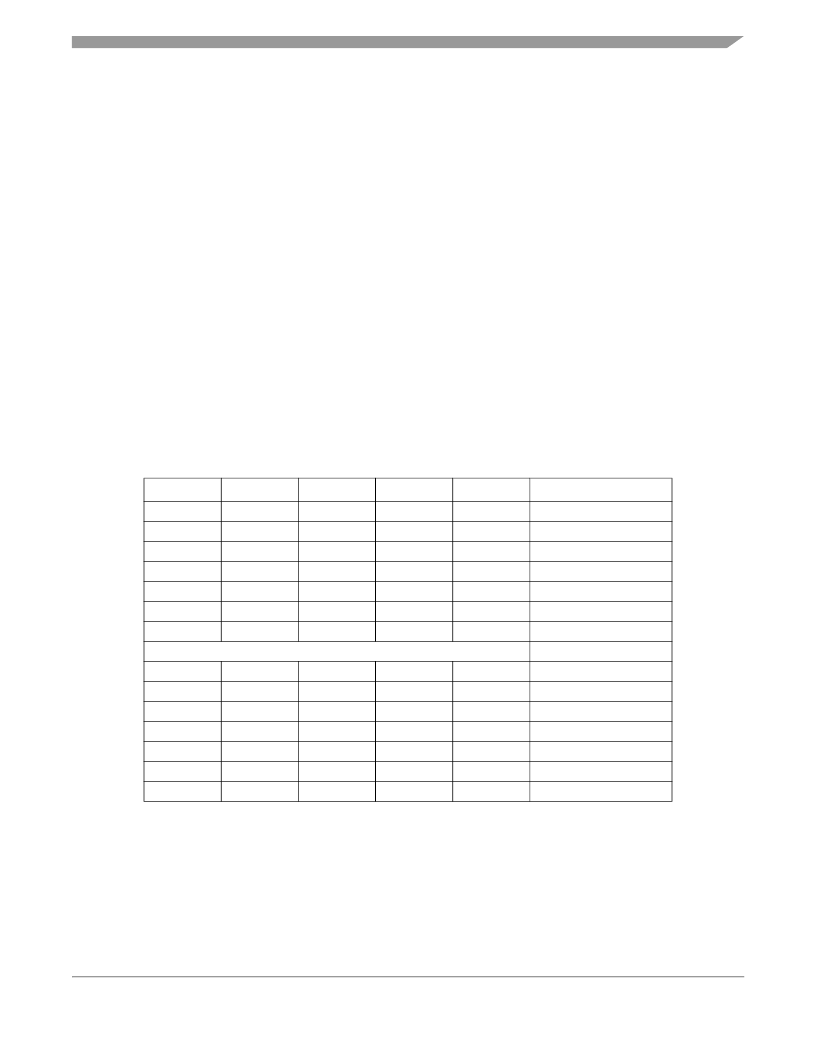

Table 3-2. Input Channel Select

ADCH4

ADCH3

ADCH2

ADCH1

ADCH0

Input Select

(1)

1. If any unused or reserved channels are selected, the resulting conversion will be unknown.

2. Requires LVI to be powered (LVIPWRD = 0, in CONFIG1)

0

0

0

0

0

AD0

0

0

0

0

1

AD1

0

0

0

1

0

AD2

0

0

0

1

1

AD3

0

0

1

0

0

AD4

0

0

1

0

1

AD5

0

0

1

1

0

Unused

Continuing through

Unused

1

1

0

0

1

Unused

1

1

0

1

0

BANDGAP REF

(2)

1

1

0

1

1

Reserved

1

1

1

0

0

Reserved

1

1

1

0

1

V

REFH

V

REFL

1

1

1

1

0

1

1

1

1

1

Low-power state

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC908QL4DT | Microcontrollers |

| MC908QL4DW | Microcontrollers |

| MC908QL4M | Microcontrollers |

| MC908QL4V | Microcontrollers |

| MC912DG128x | microcontroller unit 16BIT DEVICE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC908QL3C | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

| MC908QL3CDWE | 功能描述:8位微控制器 -MCU NITRON LIN RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| MC908QL3DT | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

| MC908QL3DW | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

| MC908QL3M | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。