- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69032 > MCIMX31DVMN5D (FREESCALE SEMICONDUCTOR INC) 32-BIT, 532 MHz, MICROPROCESSOR, PBGA473 PDF資料下載

參數(shù)資料

| 型號: | MCIMX31DVMN5D |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 532 MHz, MICROPROCESSOR, PBGA473 |

| 封裝: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, MAPBGA-473 |

| 文件頁數(shù): | 77/118頁 |

| 文件大?。?/td> | 1083K |

| 代理商: | MCIMX31DVMN5D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Electrical Characteristics

MCIMX31/MCIMX31L Technical Data, Rev. 4.3

Freescale Semiconductor

61

NOTE

HSP_CLK is the High-Speed Port Clock, which is the input to the Image

Processing Unit (IPU). Its frequency is controlled by the Clock Control

Module (CCM) settings. The HSP_CLK frequency must be greater than or

equal to the AHB clock frequency.

The SCREEN_WIDTH, SCREEN_HEIGHT, H_SYNC_WIDTH, V_SYNC_WIDTH, BGXP, BGYP and

V_SYNC_WIDTH_L parameters are programmed via the SDC_HOR_CONF, SDC_VER_CONF,

SDC_BG_POS Registers. The FW and FH parameters are programmed for the corresponding DMA

channel. The DISP3_IF_CLK_PER_WR, HSP_CLK_PERIOD and DISP3_IF_CLK_CNT_D parameters

are programmed via the DI_DISP3_TIME_CONF, DI_HSP_CLK_PER and DI_DISP_ACC_CC

Registers.

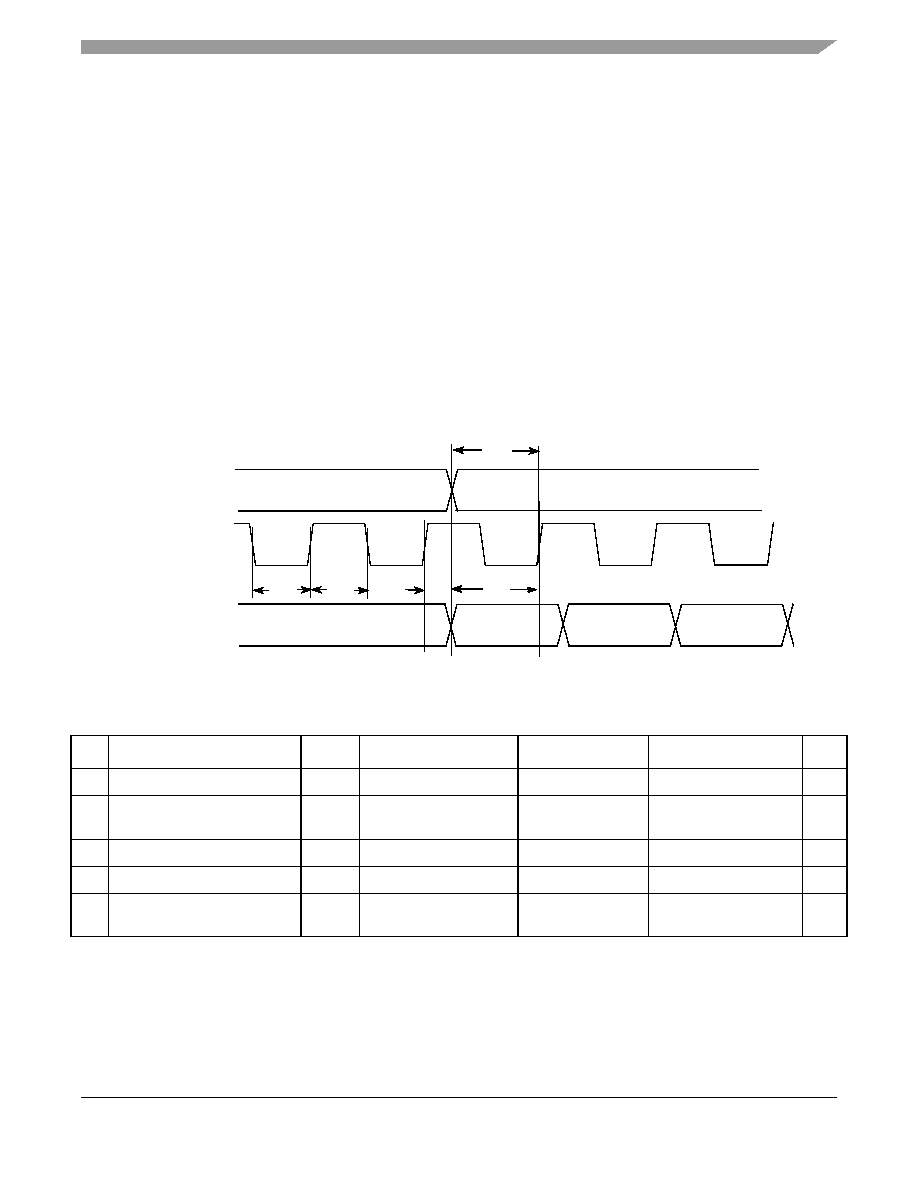

Figure 48 depicts the synchronous display interface timing for access level, and Table 47 lists the timing

parameters. The DISP3_IF_CLK_DOWN_WR and DISP3_IF_CLK_UP_WR parameters are set via the

DI_DISP3_TIME_CONF Register.

Figure 48. Synchronous Display Interface Timing Diagram—Access Level

Table 47. Synchronous Display Interface Timing Parameters—Access Level

ID

Parameter

Symbol

Min

Typ1

1 The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These

conditions may be device specific.

Max

Units

IP16 Display interface clock low time

Tckl

Tdicd–Tdicu–1.5

Tdicd2–Tdicu3

Tdicd–Tdicu+1.5

ns

IP17 Display interface clock high

time

Tckh

Tdicp–Tdicd+Tdicu–1.5

Tdicp–Tdicd+Tdicu

Tdicp–Tdicd+Tdicu+1.5

ns

IP18 Data setup time

Tdsu

Tdicd–3.5

Tdicu

—

ns

IP19 Data holdup time

Tdhd

Tdicp–Tdicd–3.5

Tdicp–Tdicu

—

ns

IP20 Control signals setup time to

display interface clock

Tcsu

Tdicd–3.5

Tdicu

—

ns

IP19

DISPB_D3_CLK

DISPB_DATA

IP18

IP20

DISPB_D3_VSYNC

IP17

IP16

DISPB_D3_DRDY

DISPB_D3_HSYNC

other controls

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCIMX31LDVKN5D | 32-BIT, 532 MHz, MICROPROCESSOR, PBGA457 |

| MCIMX31LCJKN5D | 32-BIT, 532 MHz, MICROPROCESSOR, PBGA457 |

| MCIMX512DVK8C | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA625 |

| MCIMX511DVK8C | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA625 |

| MCIMX513DVK8C | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA625 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX31DVMN5DR2 | 功能描述:處理器 - 專門應(yīng)用 2.0.1 CONSUMER FULL RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX31L | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processors |

| MCIMX31LC | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processors for Industrial and Automotive Products |

| MCIMX31LCJKN5D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processors |

| MCIMX31LCJMN4D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processors for Industrial and Automotive Products |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。