- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371087 > MCM63L918A (Motorola, Inc.) 9MBit Synchronous Late Write Fast Static RAM(8M位同步遲寫快速靜態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | MCM63L918A |

| 廠商: | Motorola, Inc. |

| 英文描述: | 9MBit Synchronous Late Write Fast Static RAM(8M位同步遲寫快速靜態(tài)RAM) |

| 中文描述: | 9MBit快速同步后寫入靜態(tài)存儲(chǔ)器(800萬位同步遲寫快速靜態(tài)內(nèi)存) |

| 文件頁數(shù): | 13/20頁 |

| 文件大?。?/td> | 412K |

| 代理商: | MCM63L918A |

MCM63L836A

MCM63L918A

13

MOTOROLA FAST SRAM

SLEEP MODE

This device is equipped with an optional sleep or low

power mode. The sleep mode pin is asynchronous and

active high. During normal operation, the ZZ pin is pulled low.

When ZZ is pulled high, the chip will enter sleep mode where

the device will meet the lowest possible power conditions.

The Sleep Mode Timing diagram shows the following modes

of operation: Normal Operation, No Read/Write Allowed, and

Sleep Mode.

Normal Operation

All inputs must meet setup and hold times prior to sleep

and tZZR nanoseconds after recovering from sleep. Clock

(CK) must also meet cycle high and low times during these

periods. Two cycles prior to sleep, initiation of either a read or

write operation is not allowed.

No Read/Write Allowed

During the period of time just prior to sleep and during

recovery from sleep, the assertion of any write or read signal

is not allowed. If a write or read operation occurs during

these periods, the memory array may be corrupted. Validity

of data out from the RAM can not be guaranteed immediately

after ZZ is asserted (prior to being in sleep). During sleep

mode recovery, the output impedance must be given

additional time above and beyond tZZR in order to match

desired impedance (see explanation in

Output Impedance

Circuitry

paragraph).

Sleep Mode

The RAM automatically deselects itself. The RAM discon-

nects its internal clock buffer. The external clock may con-

tinue to run without impacting the RAMs sleep current (IZZ).

All outputs will remain in a High–Z state while in sleep mode.

All inputs are allowed to toggle. The RAM will not be

selected, and perform any reads or writes.

SERIAL BOUNDARY SCAN TEST ACCESS PORT OPERATION

OVERVIEW

The serial boundary scan test access port (TAP) on this

RAM is designed to operate in a manner consistent with

IEEE Standard 1149.1–1990 (commonly referred to as

JTAG), but does not implement all of the functions required

for IEEE 1149.1 compliance. Certain functions have been

modified or eliminated because their implementation places

extra delays in the RAMs critical speed path. Nevertheless,

the RAM supports the standard TAP controller architecture.

The TAP controller is the state machine that controls the TAP

operation and can be expected to function in a manner that

does not conflict with the operation of devices with IEEE

1149.1 compliant TAPs. The TAP operates using conven-

tional JEDEC Standard 8–1B low voltage (3.3 V) TTL/CMOS

logic level signaling.

DISABLING THE TEST ACCESS PORT

It is possible to use this device without utilizing the TAP. To

disable the TAP controller without interfering with normal

operation of the device, TCK must be tied to VSS to preclude

mid–level inputs. TDI and TMS are designed so an undriven

input will produce a response identical to the application of a

logic 1, and may be left unconnected. But they may also be

tied to VDD through a 1 k resistor. TDO should be left uncon-

nected.

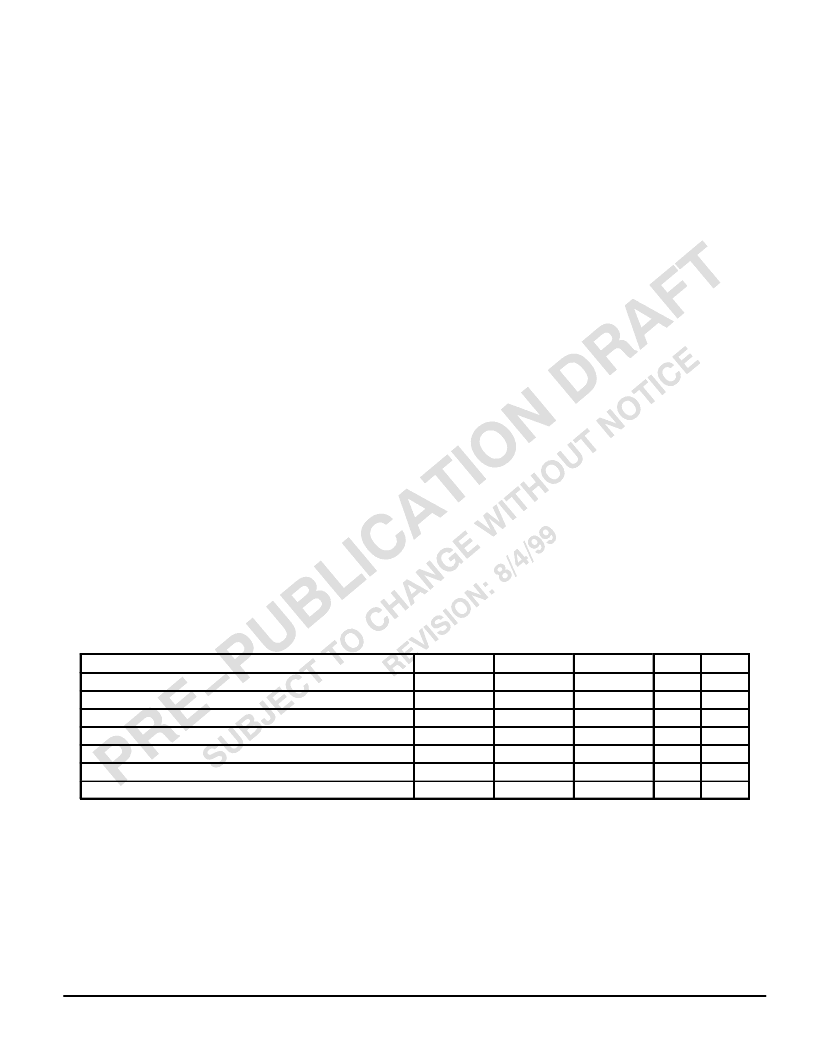

TAP DC OPERATING CHARACTERISTICS

(3.0 V

≤

VDD

≤

3.6 V, 0

°

C

≤

TA

≤

70

°

C, Unless Otherwise Noted)

Parameter

Symbol

Min

Max

Unit

Notes

Logic Input Logic High

VIH1

VIL1

Ilkg

VOL1

VOH1

VOL2

VOH2

1.2

VDD + 0.3

0.4

±

5

0.2

V

Logic Input Logic Low

–0.3

V

μ

A

V

Logic Input Leakage Current

—

1

CMOS Output Logic Low

—

2

CMOS Output Logic High

VDD – 0.2

—

—

V

3

TTL Output Logic Low

0.4

V

4

TTL Output Logic High

NOTES:

1. 0 V

≤

Vin

≤

VDD for all logic input pins.

2. IOL1

≤

100

μ

A @ VOL = 0.2 V. Sampled, not 100% tested.

3. |IOH1|

≤

100

μ

A @ VDDQ – 0.2 V. Sampled, not 100% tested.

4. IOL2

≤

8 mA @ VOL = 0.4 V.

5. |IOH2|

≤

8 mA @ VOH = 2.4 V.

2.4

—

V

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM63L836A | 8MBit Synchronous Late Write Fast Static RAM(8M位同步遲寫快速靜態(tài)RAM) |

| MCM63P631ATQ100 | 64K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P631ATQ75 | ER 4C 4#12 SKT RECP BOX |

| MCM63P631ATQ75R | MS/STANDARD CYLINDRICAL MIL-C-5015 SERIES 3102E ENVIRONMENTAL RESISTING BOX MOUNT RECEPTACLES, STRAIGHT BODY STYLE, SOLDER TERMINATION, 18 SHELL SIZE, 18-11 INSERT ARRANGEMENT, RECEPTACLE GENDER, 5 CONTACTS |

| MCM63P631A | 64K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM63P531 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P531TQ4.5 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P531TQ4.5R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P531TQ7 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

| MCM63P531TQ7R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。