- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371108 > MH64S64APFH-7L (Mitsubishi Electric Corporation) 4294967296-BIT (67108864 - WORD BY 64-BIT)SynchronousDRAM PDF資料下載

參數(shù)資料

| 型號: | MH64S64APFH-7L |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 4294967296-BIT (67108864 - WORD BY 64-BIT)SynchronousDRAM |

| 中文描述: | 4294967296位(67108864 -文字,64位)SynchronousDRAM |

| 文件頁數(shù): | 51/52頁 |

| 文件大?。?/td> | 604K |

| 代理商: | MH64S64APFH-7L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當前第51頁第52頁

MITSUBISHI LSIs

( 51

MITSUBISHI

ELECTRIC

Preliminary Spec.

Some contents are subject to change without notice.

MIT-DS-0392-0.1

MH64S64APFH-6,-6L,-7,-7L

4294967296-BIT (67108864 - WORD BY 64-BIT)SynchronousDRAM

16.Apr.2000

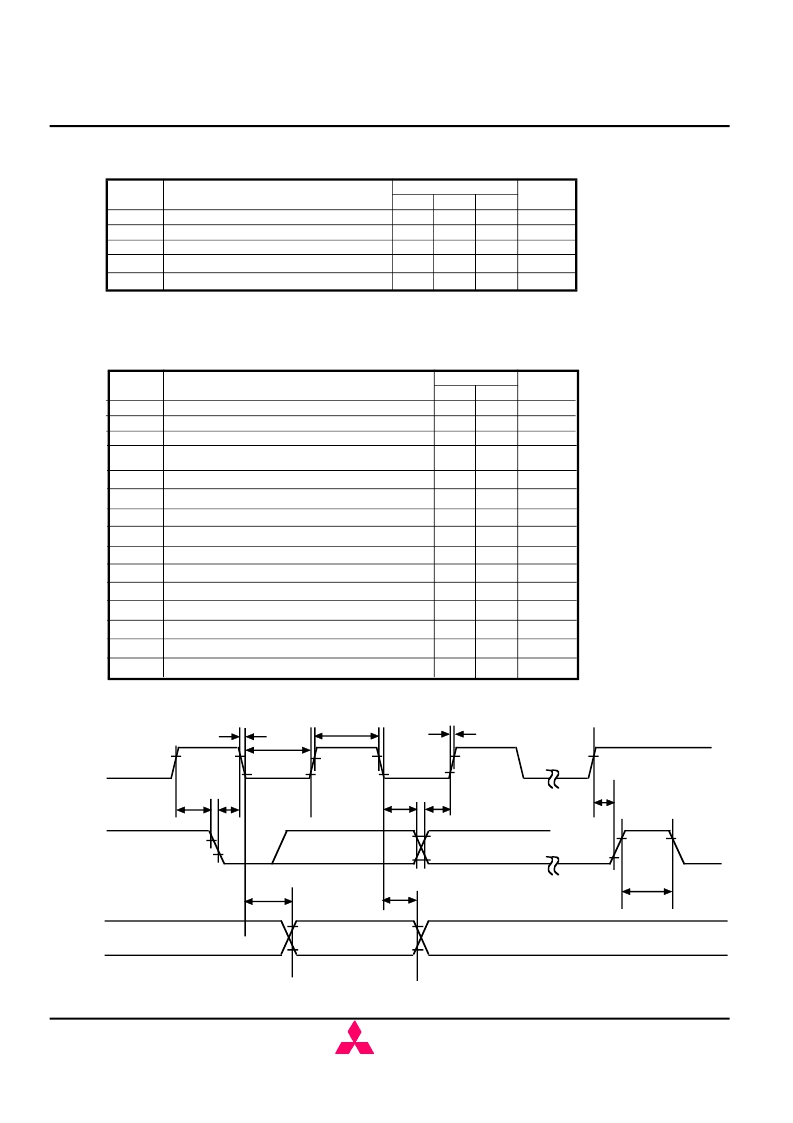

EEPROM Components A.C. and D.C. Characteristics

Limits

Typ.

3.3

0

Min.

3.0

Max.

3.6

V

V

V

V

0

0

Supply Voltage

Supply Voltage

Input High Voltage

Input Low Voltage

V

CC

V

SS

V

IH

-0.3

V

IL

V

OL

Symbol

Parameter

Units

Vccx0.3

Vddx0.7

V

Output Low Voltage

0.4

EEPROM A.C.Timing Parameters

(Ta=0 to 70C)

Limits

Min.

Max.

80

KHz

ns

us

100

7.0

6.7

SCL Clock Frequency

Noise Supression Time Constant at SCL, SDA inputs

SCL Low to SDA Data Out Valid

Time the Bus Must Be Free before a New

Transmission Can Start

fSCL

TI

TAA

TBUF

us

0.3

6.7

Symbol

Parameter

Units

4.5

us

Start Condition Hold Time

THD:STA

4.5

us

Clock Low Time

TLOW

6.7

us

us

Clock High Time

Start Condition Setup Time

THIGH

TSU:STA

0

500

us

ns

Data In Hold Time

Data In Setup Time

THD:DAT

TSU:DAT

1

1

us

SDA and SCL Rise Time

TR

ns

SDA and SCL Fall Time

TF

us

Stop Condition Setup Time

TSU:STO

6.7

ns

Data Out Hold Time

TDH

300

ms

Write Cycle Time

TWR

tWR is the time from a valid stop condition of a write sequence to the end of the EEPROM internal erase/program cycle.

300

15

SCL

SDA

IN

T

SU:STA

T

HD:STA

T

F

T

LOW

T

HIGH

T

R

T

HD:DAT

T

SU:DAT

T

SU:STO

T

BUF

SDA

OUT

T

AA

T

DH

54

相關PDF資料 |

PDF描述 |

|---|---|

| MH64S72AWJA-6 | 4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72AWJA-7 | 4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72AWJA-8 | 4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72VJG-5 | 4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72VJG-6 | 4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MH64S72AWJA-6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72AWJA-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72AWJA-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72QJA-6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT ( 64,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

| MH64S72QJA-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4,831,838,208-BIT ( 67,108,864-WORD BY 72-BIT ) Synchronous DYNAMIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。