- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69036 > MPC5125YVN400 (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 400 MHz, MICROCONTROLLER, PBGA324 PDF資料下載

參數(shù)資料

| 型號: | MPC5125YVN400 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 400 MHz, MICROCONTROLLER, PBGA324 |

| 封裝: | 23 X 23 MM, 2.25 MM HEIGHT, 1 MM PITCH, ROHS COMPLIANT, PLASTIC, MS-034AJJ-1, TEPBGA-324 |

| 文件頁數(shù): | 40/92頁 |

| 文件大小: | 640K |

| 代理商: | MPC5125YVN400 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Electrical and Thermal Characteristics

MPC5125 Microcontroller Data Sheet, Rev. 3

Freescale Semiconductor

45

4.2.3

System PLL Electrical Characteristics

4.2.4

e300 Core PLL Electrical Characteristics

The internal clocking of the e300 core is generated from and synchronized to the system clock by means of a voltage-controlled

core PLL.

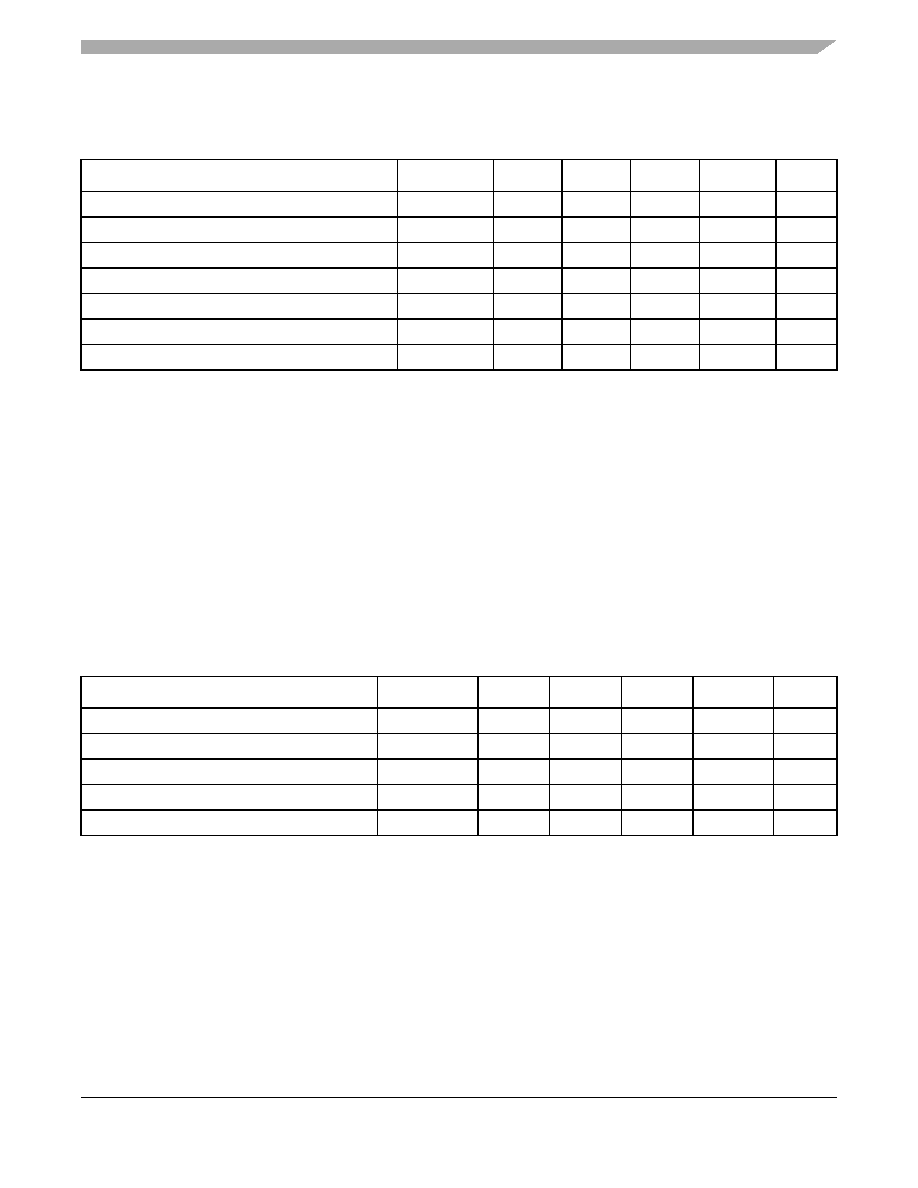

Table 15. System PLL Specifications

Characteristic

Sym

Min

Typical

Max

Unit

SpecID

Sys PLL input clock frequency1

NOTES:

1 The SYS_XTAL frequency and PLL configuration bits must be chosen such that the resulting system frequency, CPU (core)

frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.

fsys_xtal

16

33.3

67

MHz

O3.1

Sys PLL input clock jitter2

2 This represents total input jitter — short term and long term combined. Two different types of jitter can exist on the input to

CORE_SYSCLK, systemic and true random jitter. True random jitter is rejected. Systemic jitter is passed into and through the

PLL to the internal clock circuitry.

tjitter

—

10

ps

O3.2

Sys PLL VCO frequency1

fVCOsys

400

—

800

MHz

O3.3

Sys PLL VCO output jitter (Dj), peak to peak / cycle

fVCOjitterDj

—

40

ps

O3.4

Sys PLL VCO output jitter (Rj), RMS 1 sigma

fVCOjitterRj

—

12

ps

O3.5

Sys PLL relock time — after power up3

3 PLL-relock time is the maximum amount of time required for the PLL lock after a stable VDD and CORE_SYSCLK are reached

during the power-on reset sequence.

tlock1

—

200

s

O3.6

Sys PLL relock time — when power was on4

4 PLL-relock time is the maximum amount of time required for the PLL lock after the PLL has been disabled and subsequently

re-enabled during sleep modes.

tlock2

—

170

s

O3.7

Table 16. e300 PLL Specifications

Characteristic

Sym

Min

Typical

Max

Unit

SpecID

e300 frequency1, 2

NOTES:

1 The frequency and e300 PLL configuration bits must be chosen such that the resulting system frequencies, CPU (core)

frequency, and e300 PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies in

2

The following hard-coded relationship exists between fcore and fVCOcore: (fcore = fVCOcore).

fcore

200

—

400

MHz

O4.1

e300 PLL VCO frequency1

fVCOcore

400

—

800

MHz

O4.3

e300 PLL input clock frequency

fCSB_CLK

50

—

200

MHz

O4.4

e300 PLL input clock cycle time

tCSB_CLK

5

—

20

ns

O4.5

e300 PLL relock time3

3 PLL-relock time is the maximum amount of time required for the PLL lock after a stable V

DD and CORE_SYSCLK are reached

during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently

re-enabled during sleep modes.

tlock

—

200

s

O4.6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5200CVR400B | 400 MHz, MICROPROCESSOR, PBGA272 |

| MPC5533MVZ80 | FLASH, 80 MHz, MICROCONTROLLER, PBGA324 |

| MPC5533MVM40 | FLASH, 40 MHz, MICROCONTROLLER, PBGA208 |

| MPC5533MZQ66 | FLASH, 66 MHz, MICROCONTROLLER, PBGA324 |

| MPC5533MVF80 | FLASH, 80 MHz, MICROCONTROLLER, PBGA208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC5125YVN400 | 制造商:Freescale Semiconductor 功能描述:ICMICROPROCESSOR32-BITCMOSPBGA324PI |

| MPC5125YVN400R | 制造商:Freescale Semiconductor 功能描述:POWERPC EMBEDDED SOC - Tape and Reel |

| MPC5200 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Hardware Specifications |

| MPC5200B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SDRAM/DDR Memory Controller |

| MPC5200B_08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SDRAM / DDR Memory Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。