- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45359 > MPC8306SCVMADDCA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC8306SCVMADDCA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 |

| 封裝: | 19 X 19 MM, 1.61 MM HEIGHT, 0.80 MM PITCH, LEAD FREE, MAPBGA-369 |

| 文件頁(yè)數(shù): | 30/71頁(yè) |

| 文件大小: | 452K |

| 代理商: | MPC8306SCVMADDCA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 0

36

Freescale Semiconductor

Timers

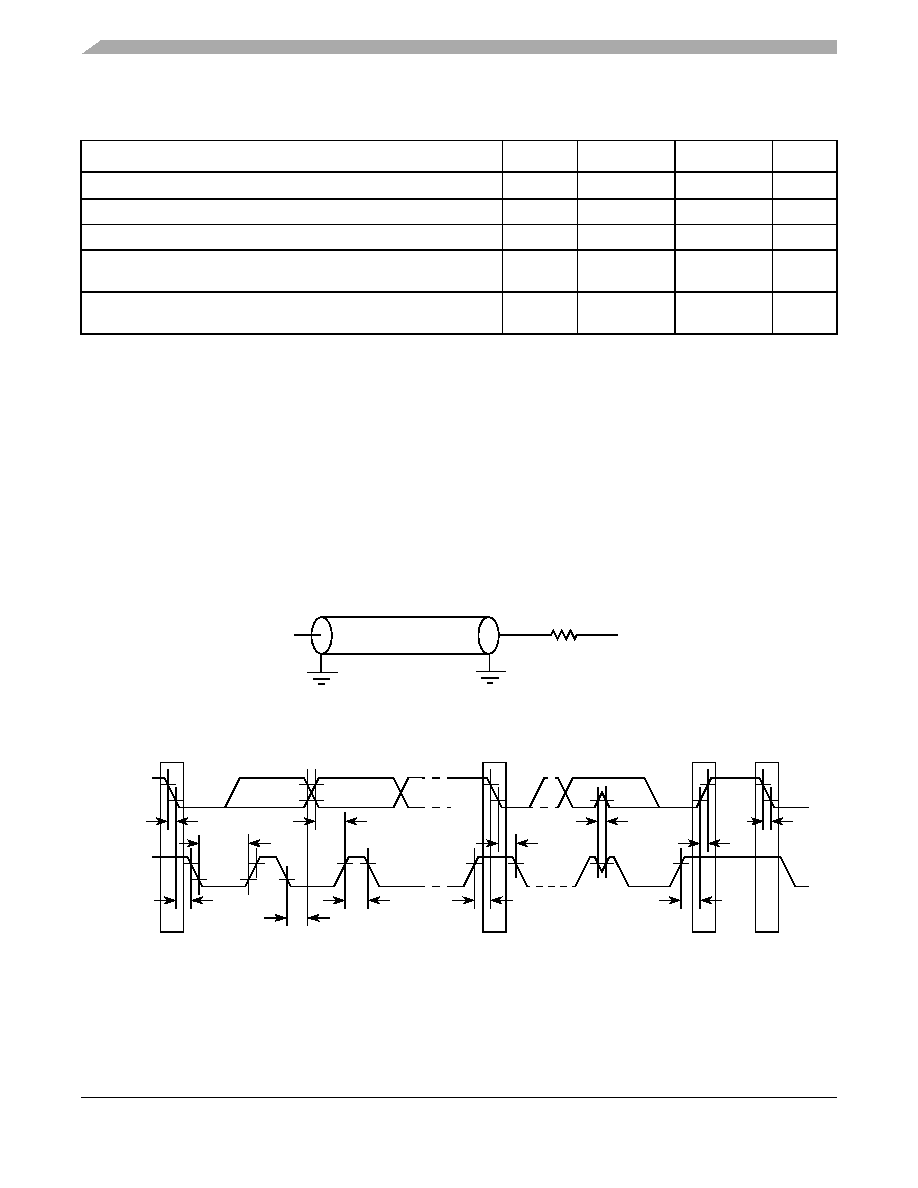

Figure 25. I2C AC Test Load

Figure 26. I2C Bus AC Timing Diagram

14 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8306S.

Fall time of both SDA and SCL signals

tI2CF

20 + 0.1 CB4

300

ns

Setup time for STOP condition

tI2PVKH

0.6

—

s

Bus free time between a STOP and START condition

tI2KHDX

1.3

—

s

Noise margin at the LOW level for each connected device (including

hysteresis)

VNL

0.1

OVDD

—V

Noise margin at the HIGH level for each connected device (including

hysteresis)

VNH

0.2

OVDD

—V

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tI2DVKH symbolizes I2C timing (I2)

with respect to the time data input signals (D) reach the valid state (V) relative to the tI2C clock reference (K) going to the high

(H) state or setup time. Also, tI2SXKL symbolizes I2C timing (I2) for the time that the data with respect to the start condition

(S) went invalid (X) relative to the tI2C clock reference (K) going to the low (L) state or hold time. Also, tI2PVKH symbolizes I2C

timing (I2) for the time that the data with respect to the stop condition (P) reaching the valid state (V) relative to the tI2C clock

reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate

letter: R (rise) or F (fall).

2.

MPC8306S provides a hold time of at least 300 ns for the SDA signal (referred to the VIH(min) of the SCL signal) to bridge

the undefined region of the falling edge of SCL.

3. The maximum tI2DVKL has only to be met if the device does not stretch the LOW period (tI2CL) of the SCL signal.

4. CB = capacitance of one bus line in pF.

Table 35. I2C AC Electrical Specifications (continued)

All values refer to VIH (min) and VIL (max) levels (see Table 34).

Parameter

Symbol1

Min

Max

Unit

Output

Z0 = 50

OVDD/2

RL = 50

Sr

S

SDA

SCL

tI2CF

tI2SXKL

tI2CL

tI2CH

tI2DXKL

tI2DVKH

tI2SXKL

tI2SVKH

tI2KHKL

tI2PVKH

tI2CR

tI2CF

PS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8306VMACDCA | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306CVMACDCA | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306VMABDCA | 32-BIT, 133 MHz, RISC PROCESSOR, PBGA369 |

| MPC8306CVMADDCA | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA369 |

| MPC8308CZQAGD | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA473 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8306SCVMAFDCA | 功能描述:微處理器 - MPU E300 MP ext tmp 333 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類(lèi)型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8306SEC | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications |

| MPC8306-SOM | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 For MPC8306 Ethernet USB 16bit RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| MPC8306SVMABDC | 制造商:Freescale Semiconductor 功能描述:MPC8306SVMABDC - Bulk |

| MPC8306SVMABDCA | 功能描述:微處理器 - MPU E300 MP 133 RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類(lèi)型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。