- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359188 > MPC852T (飛思卡爾半導(dǎo)體(中國(guó))有限公司) Hardware Specifications PDF資料下載

參數(shù)資料

| 型號(hào): | MPC852T |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | Hardware Specifications |

| 中文描述: | 硬件規(guī)格 |

| 文件頁(yè)數(shù): | 20/80頁(yè) |

| 文件大小: | 3080K |

| 代理商: | MPC852T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

MPC852T Hardware Specifications, Rev. 3.1

20

Freescale Semiconductor

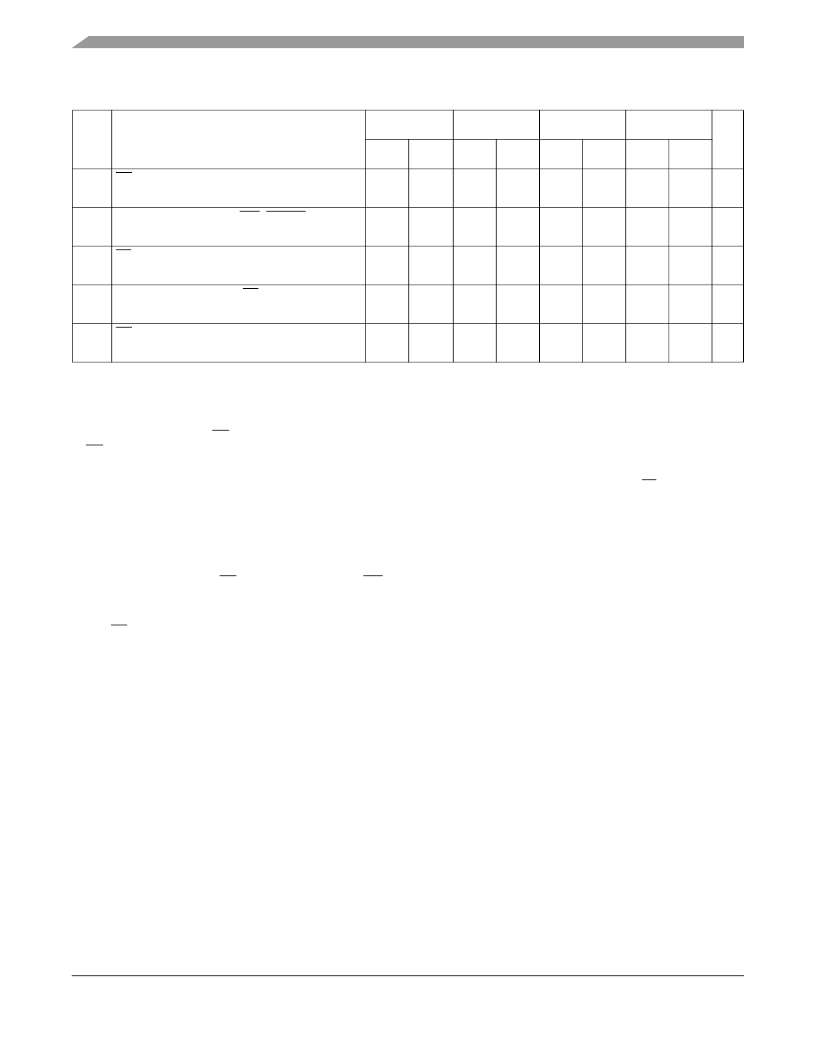

Bus Signal Timing

B39

AS valid to CLKOUT rising edge

10

(MIN = 0.00

x B1 + 7.00)

7.00

—

7.00

—

7.00

—

7.00

—

ns

B40

A(0:31), TSIZ(0:1), RD/WR, BURST, valid to

CLKOUT rising edge (MIN = 0.00 x B1 + 7.00)

7.00

—

7.00

—

7.00

—

7.00

—

ns

B41

TS valid to CLKOUT rising edge (setup time)

(MIN = 0.00 x B1 + 7.00)

7.00

—

7.00

—

7.00

—

7.00

—

ns

B42

CLKOUT rising edge to TS valid (hold time)

(MIN = 0.00 x B1 + 2.00)

2.00

—

2.00

—

2.00

—

2.00

—

ns

B43

AS negation to memory controller signals

negation (MAX = TBD)

—

TBD

—

TBD

—

TBD

—

TBD

ns

1

If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values

in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the maximum

allowed jitter on EXTAL can be up to 2%.

2

For part speeds above 50MHz, use 9.80ns for B11a.

3

The timing required for BR input is relevant when the MPC852T is selected to work with internal bus arbiter. The timing for

BG input is relevant when the MPC852T is selected to work with external bus arbiter.

4

For part speeds above 50MHz, use 2ns for B17.

5

The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is

asserted.

6

For part speeds above 50MHz, use 2ns for B19.

7

The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read

accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats where DLT3 = 1 in the

UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

8

The timing B30 refers to CS when ACS = 00 and to WE(0:3) when CSNT = 0.

9

The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37

and B38 are specified to enable the freeze of the UPM output signals as described in

Figure 18

.

10

The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified

in

Figure 21

.

Table 9. Bus Operation Timings (continued)

Num

Characteristic

33 MHz

40 MHz

50 MHz

66 MHz

Unit

Min

Max

Min

Max

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC852TVR100 | Hardware Specifications |

| MPC852TVR50 | Hardware Specifications |

| MPC852TVR66 | Hardware Specifications |

| MPC852TVR80 | Hardware Specifications |

| MPC859 | Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC852TADS | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 ADS BOARD FOR 852 RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| MPC852TADS-KIT | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 852TADS KIT RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| MPC852TCVR100A | 功能描述:微處理器 - MPU Ethernet 100 MHz RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類(lèi)型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC852TCVR50A | 功能描述:微處理器 - MPU Ethernet 50 MHz RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類(lèi)型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC852TCVR50A | 制造商:Freescale Semiconductor 功能描述:Embedded Networking Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。