- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45372 > MPC8569EVTAQLJB (FREESCALE SEMICONDUCTOR INC) RISC PROCESSOR, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MPC8569EVTAQLJB |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC PROCESSOR, PBGA783 |

| 封裝: | 29 X 29 MM, 1 MM PITCH, PLASTIC, BGA-783 |

| 文件頁數(shù): | 114/126頁 |

| 文件大小: | 2847K |

| 代理商: | MPC8569EVTAQLJB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁當(dāng)前第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

MPC8569E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 0

PCI Express

Freescale Semiconductor

88

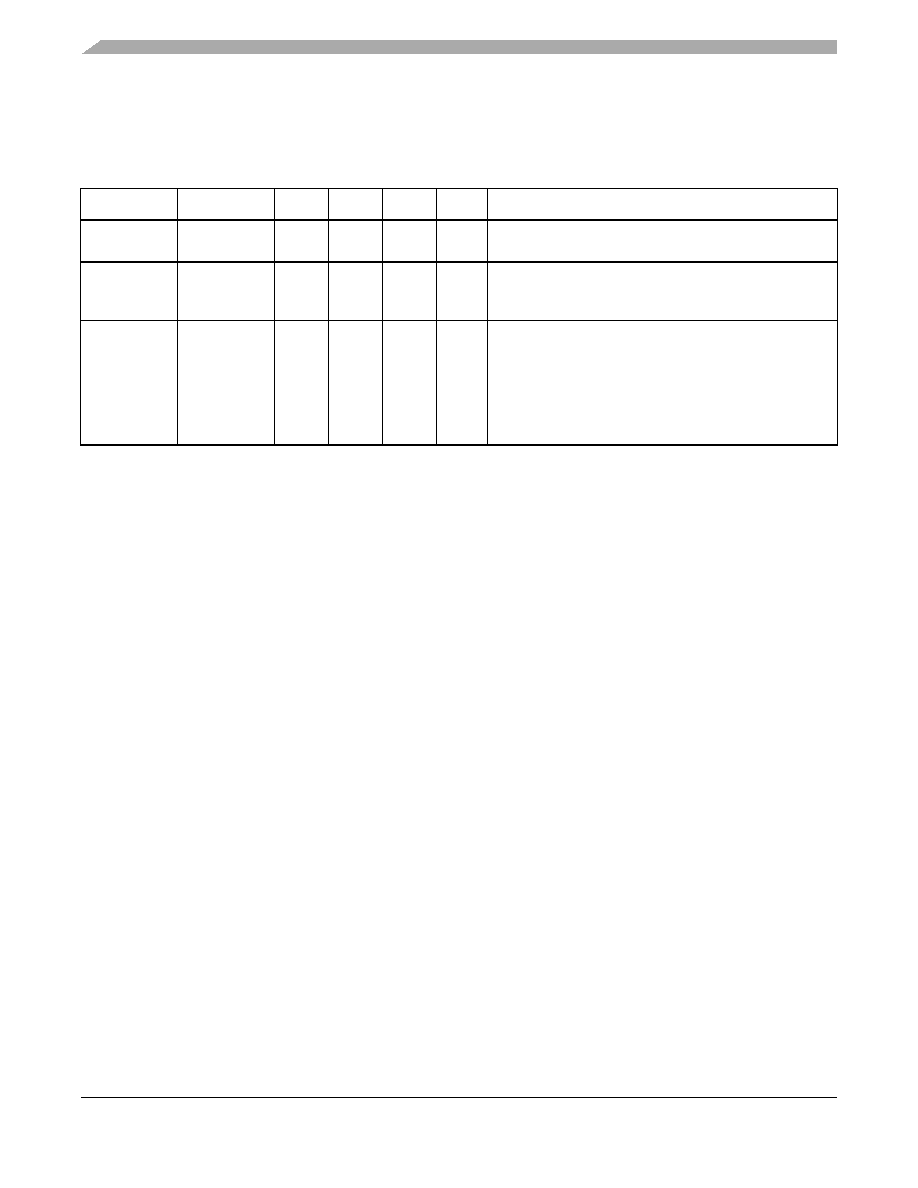

The following table defines the AC specifications for the PCI Express (2.5 Gb/s) differential input at all receivers (RXs). The

parameters are specified at the component pins. The AC timing specifications do not include RefClk jitter.

Table 51. PCI Express (2.5 Gb/s) Differential Receiver (RX) Input AC Specifications

At recommended operating conditions with ScoreVDD = 1.0 V ± 3%. and 1.1 V ± 3%

Parameter

Symbol

Min

Typ

Max

Unit

Comments

Unit interval

UI

399.88

400.00

400.12

ps

Each UI is 400 ps ± 300 ppm. UI does not account for

spread spectrum clock dictated variations. See Note 1.

Minimum

receiver eye

width

TRX-EYE

0.4

—

UI

The maximum interconnect media and transmitter jitter

that can be tolerated by the receiver can be derived as

TRX-MAX-JITTER = 1 – TRX-EYE = 0.6 UI. See Notes 2 and 3.

Maximum time

between the

jitter median

and maximum

deviation from

the median.

TRX-EYE-MEDIA

N-to-MAX-JITTER

—

0.3

UI

Jitter is defined as the measurement variation of the

crossing points (VRX-DIFFp-p = 0 V) in relation to a

recovered TX UI. A recovered TX UI is calculated over

3500 consecutive unit intervals of sample data. Jitter is

measured using all edges of the 250 consecutive UI in the

center of the 3500 UI used for calculating the TX UI.

See Notes 2, 3, and 4.

Notes:

1. No test load is necessarily associated with this value.

2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 46 must be used as

the RX device when taking measurements. If the clocks to the RX and TX are not derived from the same reference clock, the

TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

3. A TRX-EYE = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and

interconnect collected any 250 consecutive UIs. The TRX-EYE-MEDIAN-to-MAX-JITTER specification ensures a jitter distribution in

which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any

250 consecutive TX UIs. It must be noted that the median is not the same as the mean. The jitter median describes the point

in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the

clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must

be used as the reference for the eye diagram.

4. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm

using a minimization merit function. Least squares and median deviation fits have worked well with experimental and

simulated data.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8569ECVTAQLJ | RISC PROCESSOR, PBGA783 |

| MPC8572EVTARND | 32-BIT, 1067 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572ECPXARNB | 32-BIT, 1067 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572ECPXAULB | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572EPXAULD | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8569EVTAUNLB | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 8569 1.33GHz rev2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MPC8569VJAUNLB | 制造商:Freescale Semiconductor 功能描述:IC MPU PWRQUICC 1333MHZ 783FCBGA |

| MPC8569VTANKGB | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 8569 ST 800/600/400 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MPC8569VTAQLJB | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 8569 ST 1067/667/533 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MPC8569VTAUNLB | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 8569 ST 1333/667/533 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。