- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8144ETVT1000A (FREESCALE SEMICONDUCTOR INC) 133 MHz, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8144ETVT1000A |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 133 MHz, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCPBGA-783 |

| 文件頁數(shù): | 31/80頁 |

| 文件大?。?/td> | 1251K |

| 代理商: | MSC8144ETVT1000A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Electrical Characteristics

MSC8144E Quad Core Digital Signal Processor Data Sheet, Rev. 14

Freescale Semiconductor

37

2.6.3.1

Power-On Reset (PORESET) Pin

Asserting PORESET initiates the power-on reset flow. PORESET must be asserted externally for at least 32 CLKIN cycles after

VDD and VDDIO are both at their nominal levels.

2.6.3.2

Reset Configuration

The MSC8144E has two mechanisms for writing the reset configuration:

Through the I2C port

Through external pins

Through internal hard coded

Twenty-three signals (see Section 1 for signal description details) are sampled during the power-on reset sequence to define the

Reset Word Configuration Source and operating conditions:

RCW_SRC[2–0]

RC[16–0]

The RCFG_CLKIN_RNG pin must be valid during power-on or hard reset sequence. The STOP_BS pin must be always valid

and is also sampled during power-on reset sequence for RCW loading from an I2C EEPROM.

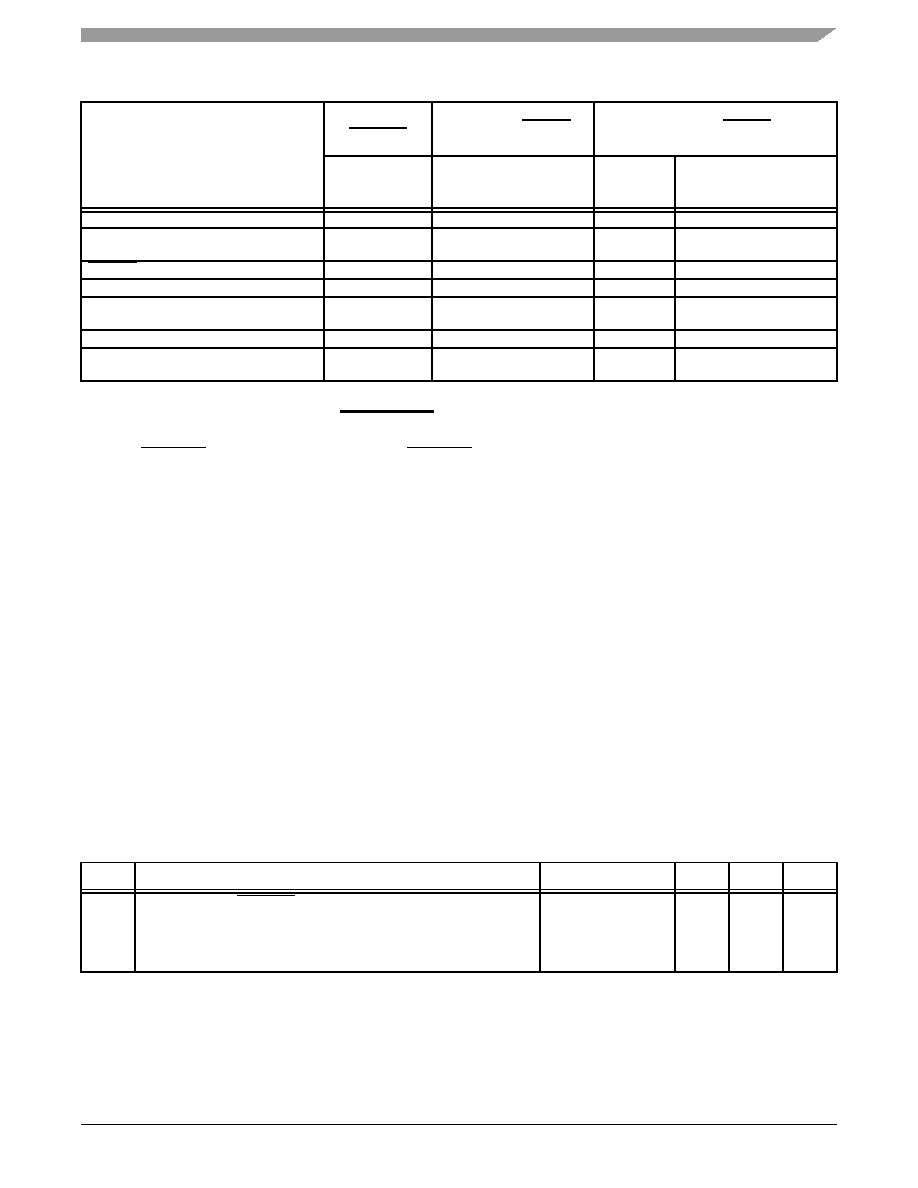

2.6.3.3 Reset Timing Tables

HRESET driven

Yes

No

IPBus modules reset (TDM, UART, SWT,

DDRC, IPBus master, GIC, HS, and GPIO)

Yes

SRESET driven

Yes

Depends on command

Extended cores reset

Yes

CLASS registers reset

Yes

Some

registers

Some registers

Timers, Performance Monitor

Yes

No

QUICC Engine Subsystem, PCI, DMA

Yes

Most

registers

Most registers

Table 19. Timing for a Reset Configuration Write

No.

Characteristics

Expression

Max

Min

Unit

1

Required external PORESET duration minimum

33 MHz <= CLKIN < 44 MHz

44 MHz <= CLKIN < 66 MHz

66 MHz <= CLKIN < 100 MHz

100 MHz <= CLKIN < 133 MHz

32/CLKIN

1280

728

485

320

727

484

320

241

ns

Table 18. Reset Actions for Each Reset Source (continued)

Reset Action/Reset Source

Power-On Reset

(PORESET)

Hard Reset (HRESET)

Soft Reset (SRESET)

External only

External or Internal

(Software Watchdog,

Software or RapidIO)

External or

internal

Software

JTAG Command:

EXTEST, CLAMP, or

HIGHZ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8144VT800B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144TVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144VT1000A | 133 MHz, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8144ETVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144ETVT800A | 制造商:Rochester Electronics LLC 功能描述: 制造商:Freescale Semiconductor 功能描述: |

| MSC8144ETVT800B | 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144EVT1000A | 制造商:Freescale Semiconductor 功能描述:DSP 32BIT 1GHZ 1000MIPS 783FCBGA - Trays |

| MSC8144EVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA 制造商:Freescale 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。