- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8144ETVT1000A (FREESCALE SEMICONDUCTOR INC) 133 MHz, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8144ETVT1000A |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 133 MHz, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCPBGA-783 |

| 文件頁數(shù): | 75/80頁 |

| 文件大?。?/td> | 1251K |

| 代理商: | MSC8144ETVT1000A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁當(dāng)前第75頁第76頁第77頁第78頁第79頁第80頁

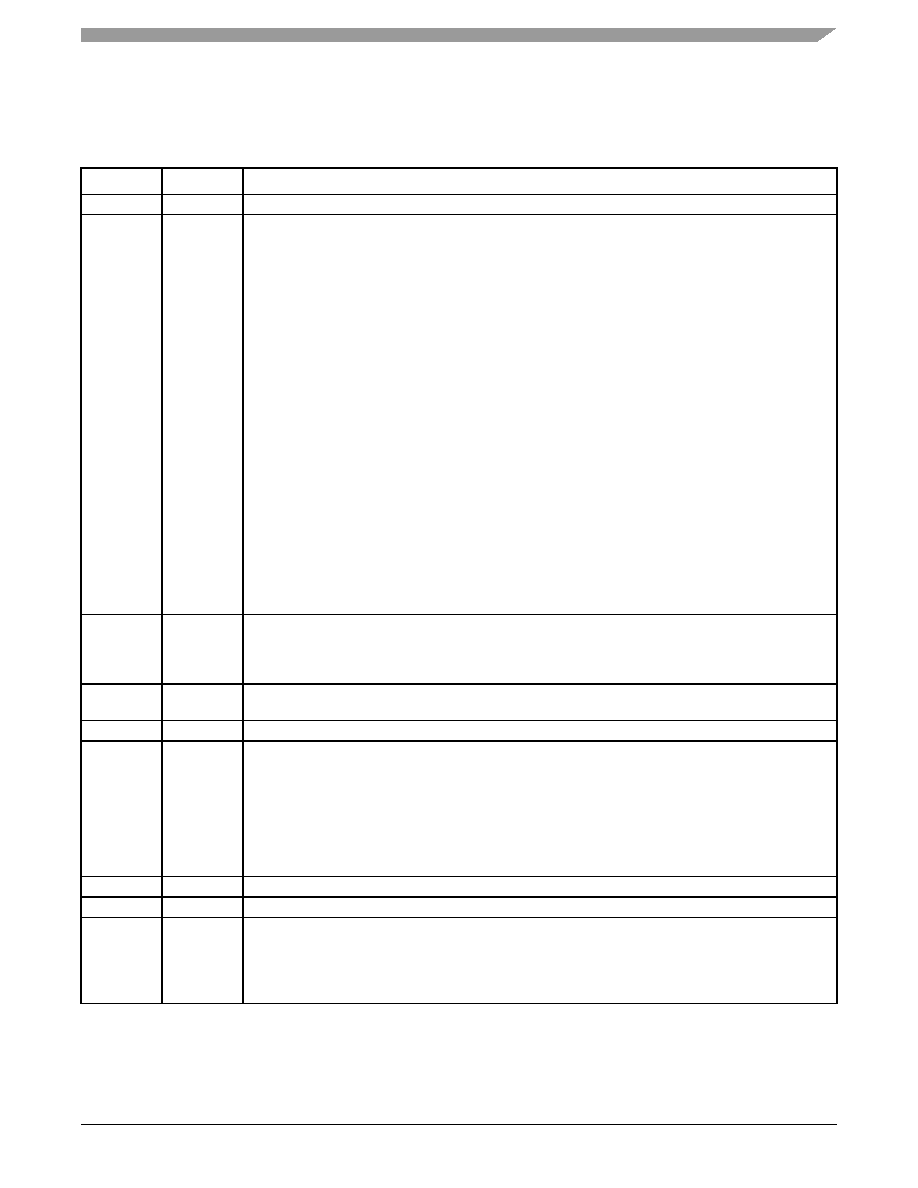

Revision History

MSC8144E Quad Core Digital Signal Processor Data Sheet, Rev. 14

Freescale Semiconductor

77

7

Revision History

Table 66 provides a revision history for this data sheet.

Revision

Date

Description

0

June. 2007 Initial public release.

1

Sep 2007

Updated M3 voltage range in Table 3.

Changed note in Table 7 for PLL power supplies.

DDR voltage designator changed from VDD to VDDDDR in Table 8, Table 10, Section 2.7.4.1, Section

2.7.4.2, and Figure 11. Changed range on IOZ in Table 8 and Table 10.

Deleted text before Table 13 and added note 2 to input pin capacitance.

Deleted text before Table 14, added a 1 to the note, and added note 1 to input pin capacitance.

Deleted Section 2.6.5 on page 32 and renumbered subsequent subsections.

Deleted text before new Section 2.6.5.1.

Added a 1 to the note in Table 15 and added note 1 to input pin capacitance.

Deleted ac voltage rows from Table 16. Added note 1 to input pin capacitance.

Changed output high and low voltage levels in Table 17 and Table 18.

Deleted text before Table 19.

Added clock skew ranges in percent in Table 21.

Changed VREF to MVREF in Table 26.

Added note 4 to Table 42. Changed tTDMSHOX value.

Changed VDD to VDDGE in Figure 27 and Figure 30.

Changed the value of the data to clock out skew in Table 51.

Changed EE pin timing in Table 55.

Changed the head for the JTAG timing section, now Section 2.7.14.

Updated JTAG timing for TCK cycle time, TCK high phase, and boundary scan input data hold time in

Table 55.

Added new Section 3.3 with guidelines for board layout for clock and timing signals. Renumbered

subsequent sections.

2

Sep 2007

Changed leakage current values in Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, and Table 19

from –10 and 10

μa to –30 and 30 μa.

Change the minimum value of tMDDVKH in Table 45 from 5 ns to 7 ns.

Updated note 1 in Table 45.

3

Oct 2007

Corrected column numbering in Figure 3 and Figure 4.

Updated SPI signal names in Table 1.

4

Oct 2007

Updated SPI signal names in Table 1.

5

Dec 2007

Changed minimum voltage level for VDDM3 to 1.213 (1.25 – 3%) in Table 3.

Added POS to titles in Section 2.6.6.

Added ATM and POS to headings in Section 2.7.11. Changed characteristics to generic input/output in

Replaced Sections 2.7.13 and 2.7.14 with new Section 2.7.13. Renumbered subsequent sections, tables,

and figures.

Added POS to all UTOPIA references in Section 3.4.5.

6

Dec 2007

7

Mar 2008

Changed description of Table 16 in Section 2.7.2.

8

Apr 2008

Changed the first sentence in Section 3.4.8 to reflect that Table 70 indicates what to do with pins if they

are “not” required by the design. Changed the Pin Connection for GPIO[0–31] to GND.

Updated ordering information in Section 4.

Multiple corrections of minor punctuation errors.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8144VT800B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144TVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144VT1000A | 133 MHz, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8144ETVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144ETVT800A | 制造商:Rochester Electronics LLC 功能描述: 制造商:Freescale Semiconductor 功能描述: |

| MSC8144ETVT800B | 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA |

| MSC8144EVT1000A | 制造商:Freescale Semiconductor 功能描述:DSP 32BIT 1GHZ 1000MIPS 783FCBGA - Trays |

| MSC8144EVT1000B | 制造商:Freescale Semiconductor 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each 制造商:Freescale Semiconductor 功能描述:DSP 32-BIT 1GHZ 1000MIPS 783-PIN FCBGA EACH - Bulk 制造商:Freescale Semiconductor 功能描述:ENCRYPTION PACSUN R2.1 783FCPBGA 制造商:Freescale 功能描述:DSP 32-Bit 1GHz 1000MIPS 783-Pin FCBGA Each |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。