- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8254SVT800B (FREESCALE SEMICONDUCTOR INC) 0-BIT, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8254SVT800B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件頁數(shù): | 19/68頁 |

| 文件大小: | 909K |

| 代理商: | MSC8254SVT800B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MSC8254 Quad-Core Digital Signal Processor Data Sheet, Rev. 4

Electrical Characteristics

Freescale Semiconductor

26

This section describes the DC electrical characteristics for the MSC8254.

2.5.1

DDR SDRAM DC Electrical Characteristics

This section describes the DC electrical specifications for the DDR SDRAM interface of the MSC8254.

Note:

DDR2 SDRAM uses VDDDDR(typ) = 1.8 V and DDR3 SDRAM uses VDDDDR(typ) = 1.5 V.

2.5.1.1

DDR2 (1.8 V) SDRAM DC Electrical Characteristics

Table 6 provides the recommended operating conditions for the DDR SDRAM controller when interfacing to DDR2 SDRAM.

Note:

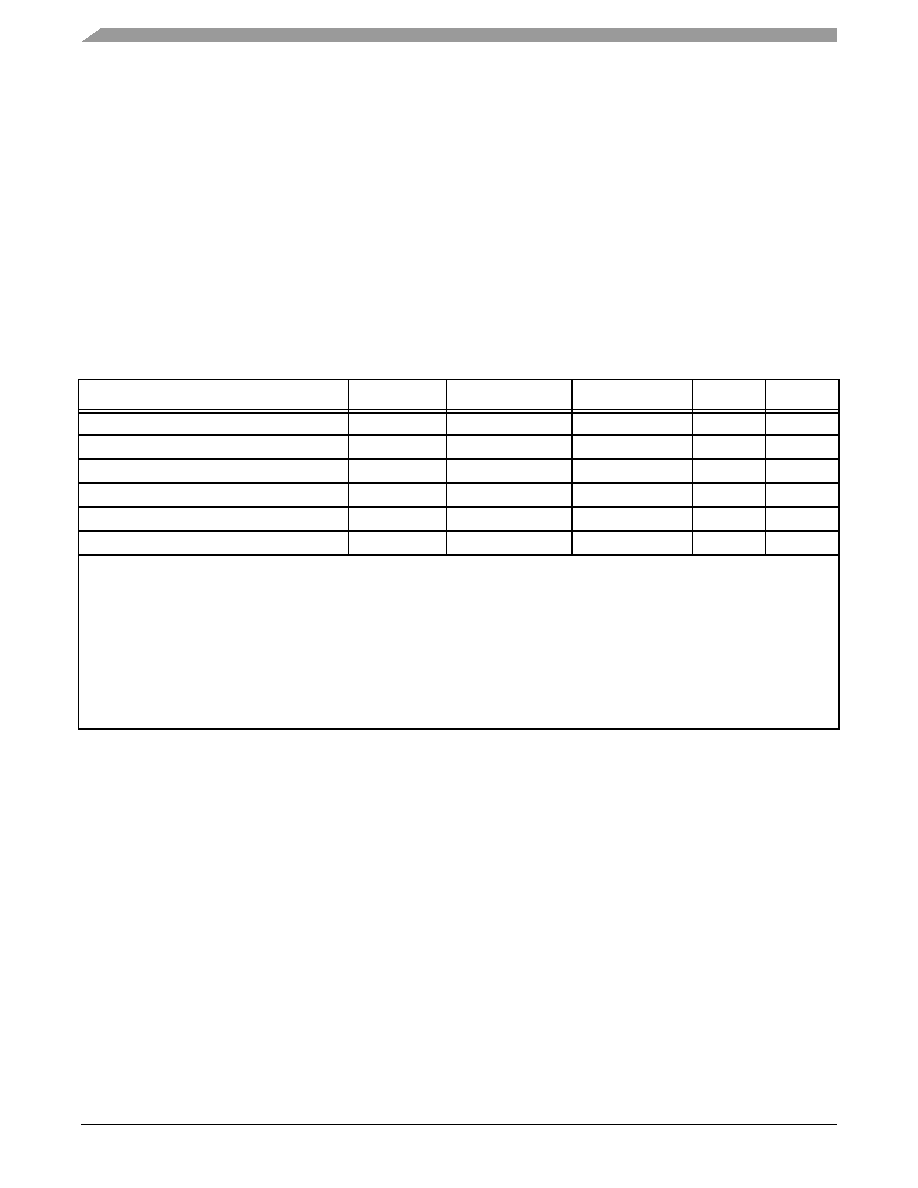

Table 6. DDR2 SDRAM Interface DC Electrical Characteristics

Parameter/Condition

Symbol

Min

Max

Unit

Notes

I/O reference voltage

MVREF

0.49

× VDDDDR

0.51

× VDDDDR

V2, 3, 4

Input high voltage

VIH

MVREF + 0.125

VDDDDR +0.3

V

5

Input low voltage

VIL

–0.3

MVREF – 0.125

V

5

I/O leakage current

IOZ

–50

50

μA6

Output high current (VOUT (VOH) = 1.37 V)

IOH

–13.4

—

mA

7

Output low current (VOUT (VOL) = 0.33 V)

IOL

13.4

—

mA

7

Notes:

1.

VDDDDR is expected to be within 50 mV of the DRAM VDD supply voltage at all times. The DRAM and memory controller can

use the same or different sources.

2.

MVREF is expected to be equal to 0.5 × VDDDDR and to track VDDDDR DC variations as measured at the receiver. Peak-to-peak

noise on MVREF may not exceed ±2% of the DC value.

3.

VTT is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal

to MVREF with a minimum value of MVREF – 0.4 and a maximum value of MVREF + 0.04 V. VTT should track variations in the

DC-level of MVREF.

4.

The voltage regulator for MVREF must be able to supply up to 300 μA.

5.

Input capacitance load for DQ, DQS, and DQS signals are available in the IBIS models.

6.

Output leakage is measured with all outputs are disabled, 0 V

≤ V

OUT

≤ V

DDDDR.

7.

Refer to the IBIS model for the complete output IV curve characteristics.

相關PDF資料 |

PDF描述 |

|---|---|

| MSC8254TVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256SVT800B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256TVT800B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256SVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSM5547RS | 0 TIMER(S), REAL TIME CLOCK, PDIP42 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8254TVT1000B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore 4-core RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MSC8254TVT800B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore 4-core RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| MSC8256 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Six-Core Digital Signal Processor |

| MSC8256_11 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Six-Core Digital Signal Processor |

| MSC8256ETAG1000B | 制造商:Freescale Semiconductor 功能描述:DSP,STARCORE, 6-CORE - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。