- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45393 > MSM80C88A-10JS (OKI ELECTRIC INDUSTRY CO LTD) 8-BIT, 10 MHz, MICROPROCESSOR, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | MSM80C88A-10JS |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 10 MHz, MICROPROCESSOR, PQCC44 |

| 封裝: | 0.650 X 0.650 INCH, 1.27 MM PITCH, PLASTIC, QFJ-44 |

| 文件頁數(shù): | 6/37頁 |

| 文件大?。?/td> | 267K |

| 代理商: | MSM80C88A-10JS |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

14/37

Semiconductor

MSM80C88A-10RS/GS/JS

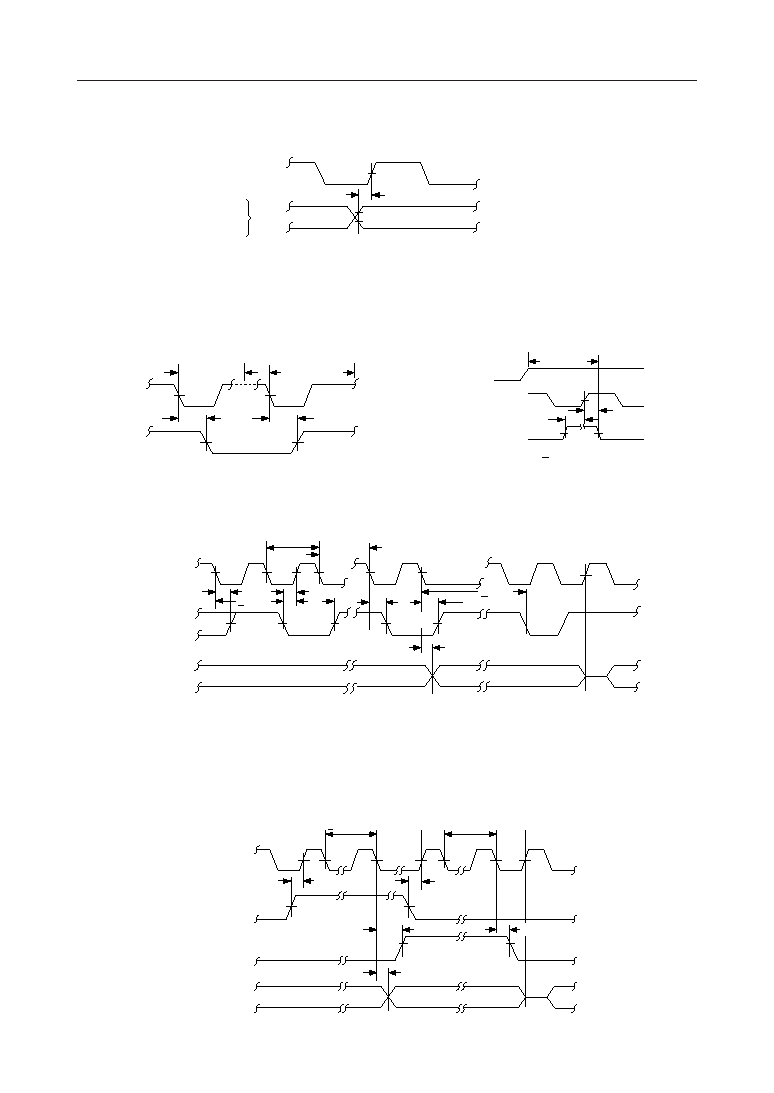

Asynchronous Signal Recognition

Hold/Hold Acknowledge Timing (Minimum Mode Only)

Request/Grant Sequence Timing (Maximum Mode Only)

CLK

Signal

NMI

INTR

TEST

tINVCH (See NOTE 1)

NOTE: 1 Setup requirements for asynchronous

signals only to guarantee recognition

at next CLK

Bus Lock Signal Timing (Maximum Mode Only)

Reset Timing

CLK

LOCK

tCLAV

Any CLK Cycle

tCLAV

≥ 50msec

tDVCL

CLK

tCLDX

Reset

VCC

≥ 4 CLK Cycles

CLK

HOLD

AD7 - AD0, A15 - A8

A19/S6 - A16/S3

RD

IO/M

DT/R, WR, DEN

HLDA

MSM80C88A-10

Coprocessor

MSM80C88A-10

1 CLK Cycle

1 or 2 Cycles

tHVCH

tCLHAV

tCLAZ

Any CLK Cycle

CLK

RQ/GT

AD7 - AD0, A15 - A8

A19/S6 - A16/S3

S2, S1, S0,

RD, COCK

tCLGH

≥ tCLCL

tGVCH

tCHGX

tCLGL

≥ tCLCL

tCLGH

Previous Grant

tCLAZ

Pulse 3

Coprocessor

Release

MSM80C88A-10

Coprocessor

MSM80C88A-10

(See NOTE 1)

NOTE: 1 The coprocessor may not drive the busses outside

the region shown without risking contention

Pulse 1

Coprocessor

RQ

Pulse 2

MSM80C88

GT

> 0 CLK Cycle

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM80C88A-10GS-K | 8-BIT, 10 MHz, MICROPROCESSOR, PQFP56 |

| MSM81C55-5GS-2K | 22 I/O, PIA-GENERAL PURPOSE, PQFP44 |

| MSM82C51A-2GS-VK | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PDSO32 |

| MSM82C51A-2JS | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PQCC28 |

| MSM82C51A-2GS-K | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM80C88A-10RS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:8-Bit CMOS MICROPROCESSOR |

| MSM80C88A2JS | 制造商:OKI 功能描述:* |

| MSM8128 | 制造商:MOSAIC 制造商全稱:MOSAIC 功能描述:128K x 8 SRAM |

| MSM8128V-10 | 制造商:MOSAIC 制造商全稱:MOSAIC 功能描述:128K x 8 SRAM |

| MSM8128V-12 | 制造商:MOSAIC 制造商全稱:MOSAIC 功能描述:128K x 8 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。