- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224505 > MT41J512M4JE-187EIT:A 64M X 4 DDR DRAM, PBGA82 PDF資料下載

參數(shù)資料

| 型號(hào): | MT41J512M4JE-187EIT:A |

| 元件分類: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, PBGA82 |

| 封裝: | 12.50 X 15 MM, LEAD FREE, FBGA-82 |

| 文件頁(yè)數(shù): | 10/11頁(yè) |

| 文件大?。?/td> | 288K |

PDF: 09005aef826aaadc/Source: 09005aef826a65af

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2Gb DDR3 SDRAM.fm - Rev. C 12/07 EN

8

2006 Micron Technology, Inc. All rights reserved.

2Gb: x4, x8 DDR3 SDRAM

Mode Register (MR) Definition

Advance

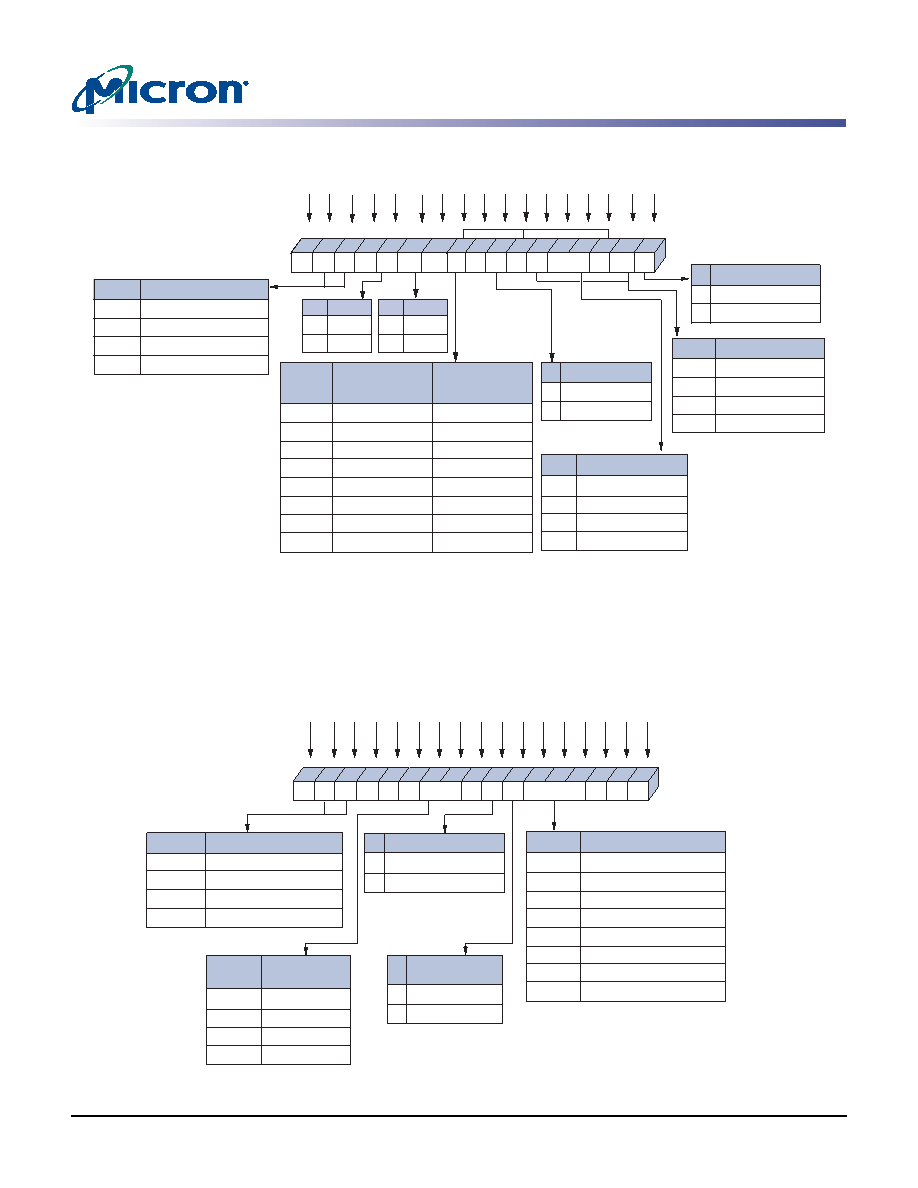

Figure 4:

Mode Register 1 (MR1) Definition

Notes:

1. MR1[16, 13, 10, 8] are reserved for future use and must be programmed to “0.”

2. During write leveling, if MR1[7] and MR1[12] are “1,” then all RTT_NOM values are available

for use.

3. During write leveling, if MR1[7] is a “1” MR1[12] is a “0,” then only RTT_NOM write values

are available for use.

Figure 5:

Mode Register 2 (MR2) Definition

Notes:

1. MR2[16,13:11, 8, 2:0] are reserved for future use and must all be programmed to “0.”

AL

RTT

Q Off

A9

A7 A6 A5 A4 A3

A8

A2

A1 A0

Mode register 1 (MR1)

Address bus

9

7

6

5

4

3

8

2

1

0

A10

A12 A11

BA0

BA1

10

11

12

13

M0

0

1

DLL Enable

Enable (normal)

Disable (DLL off mode)

M5

0

1

Output Drive Strength

RZQ/6 (40

Ω [NOM])

RZQ/7 (34

Ω [NOM])

Reserved

14

WL

1

0

M14

0

1

0

1

M15

0

1

Mode Register

Mode register set 0 (MR0)

Mode register set 1 (MR1)

Mode register set 2 (MR2)

Mode register set 3 (MR3)

ODS DLL

RTT

TDQS

M12

0

1

Q Off

Enabled

Disabled

BA2

15

01

M7

0

1

Write Levelization

Disable (normal)

Enable

Additive Latency (AL)

Disabled (AL = 0)

AL = CL - 1

AL = CL - 2

Reserved

M3

0

1

0

1

M4

0

1

RTT

ODS

M1

0

1

0

1

A13

16

01

M11

0

1

TDQS

Disabled

Enabled

01

RTT_NOM (ODT)2

Non-Writes

RTT_NOM disabled

RZQ/4 (60

Ω [NOM])

RZQ/2 (120

Ω [NOM])

RZQ/6 (40

Ω [NOM])

RZQ/12 (20

Ω [NOM])

RZQ/8 (30

Ω [NOM])

Reserved

RTT_NOM (ODT)3

Writes

RTT_NOM disabled

RZQ/4 (60

Ω [NOM])

RZQ/2 (120

Ω [NOM])

RZQ/6 (40

Ω [NOM])

n/a

Reserved

M2

0

1

0

1

0

1

0

1

M6

0

1

0

1

M9

0

1

M14

0

1

0

1

M15

0

1

Mode Register

Mode register set 0 (MR0)

Mode register set 1 (MR1)

Mode register set 2 (MR2)

Mode register set 3 (MR3)

A9

A7 A6 A5 A4 A3

A8

A2 A1 A0

Mode register 2 (MR2)

Address bus

97

6

54

3

8

2

1

0

A10

A12 A11

BA0

BA1

10

11

12

13

14

15

1

CWL

01

0

BA2

ASR

16

01

A13

01

01 01 01

01

SRT

RTT_WR

M6

0

1

Auto Self Refresh

(Optional)

Disabled: Manual

Enabled: Automatic

M7

0

1

Self Refresh Temperature

Normal (0°C to 85°C)

Extended (0°C to 95°C)

CAS Write Latency (CWL)

5 CK (tCK

≥ 2.5ns)

6 CK (2.5ns

> tCK ≥ 1.875ns)

7 CK (1.875ns

> tCK ≥ 1.5ns)

8 CK (1.5ns

> tCK ≥ 1.25ns)

Reserved

M3

0

1

0

1

0

1

0

1

M4

0

1

0

1

M5

0

1

M9

0

1

0

1

M10

0

1

Dynamic ODT

( RTT_WR )

RTT_WR disabled

RZQ/4

RZQ/2

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT42C8255RG-7TR | 256K X 8 VIDEO DRAM, 70 ns, PDSO40 |

| MT46V32M16TG-75ELIT | 32M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| MT46V32M16BN-5BLIT | 32M X 16 DDR DRAM, 0.7 ns, PBGA60 |

| MT46V32M81AZ4-6T:G | 32M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| MT47H128M8HV-187ELIT:E | 128M X 8 DDR DRAM, 0.35 ns, PBGA60 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT41J512M4V79D3WC1 | 制造商:Micron Technology Inc 功能描述:512MX4 DDR3 SDRAM DIE-COM COMMERCIAL 1.5V - Trays |

| MT41J512M4V89C3WC1 | 制造商:Micron Technology Inc 功能描述:512MX4 DDR3 SDRAM DIE-COM COMMERCIAL 1.5V - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。