- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90732AP (Mitel Networks Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號(hào): | MT90732AP |

| 廠商: | Mitel Networks Corporation |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 4/8頁 |

| 文件大?。?/td> | 61K |

| 代理商: | MT90732AP |

MT90732

CMOS

Advance Information

5-18

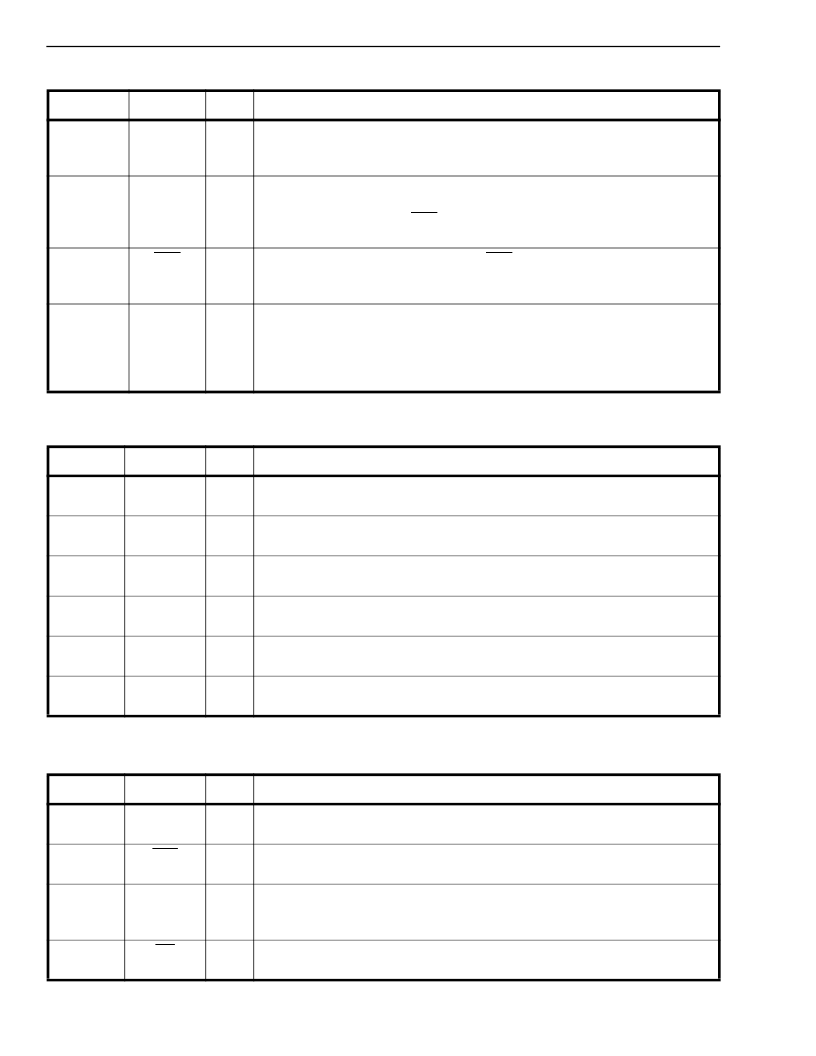

Note: I = Input; O = Output; P = Power

Note: I = Input; O = Output; P = Power

56

XNIB0/XSD

I

Transmit Nibble Bit 0/Transmit Serial Data.

In the nibble-parallel mode, bit 0

is the least significant bit in the nibble. For a serial interface, the input must

consist of all the bits in the frame.

57

XCK

I

Transmit Clock.

For the terminal side nibble-parallel interface, the XCK is

used for all transmit timing functions, including deriving the nibble output clock

(XNC) and framing pulse (XNF).For the serial interface, this clock may be

derived from the transmit reference generator clock output (TCOUT).

58

XNF

O

Transmit Nibble Framing Pulse.

The XNF and clock signal (XNC) are pro-

vided for multiplexing nibble data into the E2/E3 Framer from external circuitry.

The negative framing pulse identifies the first bit in the frame.

59

XNC/TCOU

T

O

Transmit Nibble Clock/Transmit Reference Generator Clock Out.

The

XNC is derived from the transmit clock (XCK) and is used as a time base for

clocking data out of the external multiplexer and into the E2/E3 Framer. XNC is

gapped during the framing pattern, service bit and BIP-4 bit times. TCOUT is

derived from the input clock (TCIN), and has the same duty cycle.

Service Bit Interface

Pin #

Name

I/O/P

Description

9

ROD

O

Receive Service Data Bits.

These service bits are clocked out of E2/E3

Framer on positive transitions of clock signal (ROC).

10

ROC

O

Receive Service Bits Clock.

A gapped clock that clocks out the service bits.

The clock is active only for clocking out the receive service data bits(ROD).

11

ROF

O

Receive Service Bits Framing Pulse.

A positive framing pulse that is syn-

chronous with the first bit in the frame.

27

TOD

I

Transmit Service Data Bits.

The service bits are clocked into E2/E3 Framer

on positive transitions of clock signal (TOC).

28

TOC

O

Transmit Service Bits Clock.

A gapped clock that clocks in the service bits.

The clock is active only for clocking in the transmit service data bits (TOD).

29

TOF

O

Transmit Service Bits Framing Pulse.

A positive framing pulse that is syn-

chronous with the first bit in the frame.

Microprocessor Interface

Pin #

Name

I/O/P

Description

36-43

AD(7-0)

I/O

Address/Data Bus.

These leads constitute the time-multiplexed address and

data bus for accessing the registers which reside in the E2/E3F.

44

SEL

I

Select.

A low enables the microprocessor to access the E2/E3F memory map

for control, status, and alarm information.

45

ALE

I

Address Latch Enable.

An active high signal generated by the microproces-

sor. Used by the microprocessor to hold an address stable during a read/write

bus cycle.

46

RD

I

Read.

An active low signal generated by the microprocessor for reading the

registers which reside in the memory map.

Terminal Interface

Pin #

Name

I/O/P

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90732 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT9074 | T1/E1/J1 Single Chip Transceiver |

| MT9074AL | T1/E1/J1 Single Chip Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90733 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS DS3 Framer (DS3F) |

| MT90733AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS DS3 Framer (DS3F) |

| MT9074 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 Single Chip Transceiver |

| MT9074AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 5V 100MQFP - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。