- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT9075AP (Mitel Networks Corporation) E1 Single Chip Transceiver PDF資料下載

參數(shù)資料

| 型號: | MT9075AP |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | E1 Single Chip Transceiver |

| 中文描述: | 素E1單芯片收發(fā)器 |

| 文件頁數(shù): | 55/78頁 |

| 文件大小: | 1008K |

| 代理商: | MT9075AP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

Preliminary Information

MT9075A

4-183

Bit

Name

Functional Description

7 - 2

---

Unused

1 - 0

LEC9

-

LEC8

Latched E bit error counter (the

most significant two bits).

These

bits are sampled every second by

the internal one second timer.

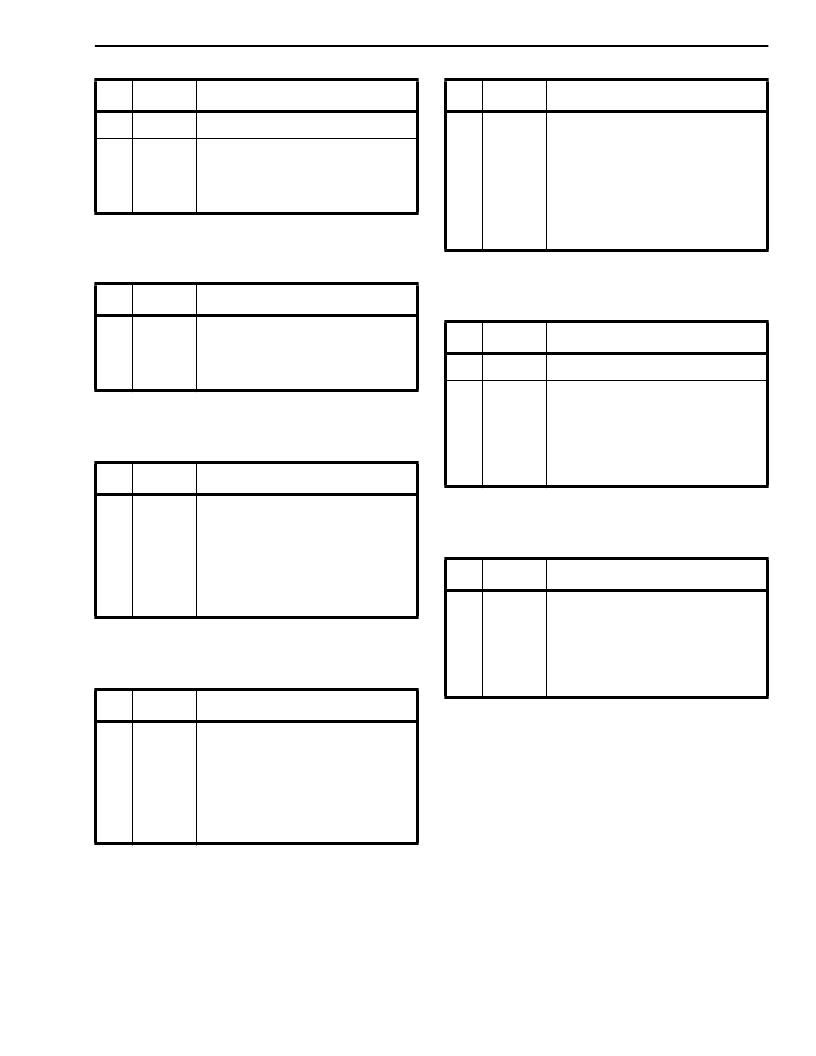

Table 71 - Latched E-bit Error Counter

(Page 09H, Address 10H)

Bit

Name

Functional Description

7 - 0

LEC7

-

LEC0

Latched E Bit Error Counter (the

least significant eight bits).

These

bits are sampled every second by

the internal one second timer.

Table 72 - Latched E-bit Error Counter

(Page 09H, Address 11H)

Bit

Name

Functional Description

7 - 0

LEFAS7

-

LEFAS0

Latched Errored FAS Counter.

An

8 bit counter that is incremented

once for every receive frame

alignment signal that contains one

or more errors. These bits are

sampled every second by the

internal one second timer.

Table 73 - Latched Errored Frame Alignment

Signal Counter (Page 09H, Address 12H)

Bit

Name

Functional Description

7 - 0

LBPV15

-

LBPV8

Latched BPV Counter (most

significant 8 bits).

counter is incremented once for

every

bipolar

received. These bits are sampled

every second by the internal one

second timer.

The BPV

violation

error

Table 74 - Most Significant Bits of the Latched

BPV Counter (Page 09H, Address 13H)

Bit

Name

Functional Description

7 - 0

LBPV7

-

LBPV0

Latched

significant 8 bits).

The least

significant eight bits of a 16 bit

counter that is incremented once for

every

bipolar

received. These bits are sampled

every second by the internal one

second timer.

BPV

Counter

(least

violation

error

Table 75 - Least Significant Bits of the Latched

BPV Counter (Page 09H, Address 14H)

Bit

Name

Functional Description

7 - 2

---

Unused

1 - 0

LCC9

-

LCC8

Latched CRC-4 Error Counter

(Bits 9 & 8).

These are the most

significant two bits of the CRC-4

error counter. These bits are

sampled every second by the

internal one second timer.

Table 76 - Latched CRC-4 Error Counter

(Page 09H, Address 15H)

Bit

Name

Functional Description

7 - 0

LCC7

-

LCC0

Latched CRC-4 Error Counter

(Bits 7-0)

. These are the least

significant eight bits of the CRC-4

error counter. These bits are

sampled every second by the

internal one second timer.

Table 77 - Latched CRC-4 Error Counter

(Page 09H, Address 16H)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9075BL | E1 Single Chip Transceiver |

| MT9075BP | E1 Single Chip Transceiver |

| MT9075B-1 | E1 Single Chip Transceiver |

| MT9075 | () |

| MT9076 | T1/E1/J1 3.3V Single Chip Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9075B | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:E1 Single Chip Transceiver |

| MT9075B-1 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:E1 Single Chip Transceiver |

| MT9075BL | 制造商:Microsemi Corporation 功能描述:FRAMER E1 5V 100MQFP - Trays |

| MT9075BL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 5V 100MQFP - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TXRX SGL E1 W/LIU 100MQFP 制造商:Microsemi Corporation 功能描述:IC TXRX SGL E1 W/LIU 100MQFP |

| MT9075BP | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。